#### Lightweight PRNG for Low-Cost Passive RFID Security Improvement

By Joan Melià-Seguí

A Dissertation Submitted in Partial Fulfillment of the Requirements for the PhD Degree

> Advisors: Dr. Joaquin Garcia-Alfaro Dr. Jordi Herrera-Joancomartí

> > April 2011

KISON Research Group Internet Interdisciplinary Institute Universitat Oberta de Catalunya

By Joan Melià Seguí

Cover: Berta Mir Daza

2011

Als meus pares, i a la meva germana, pel seu suport i amor des del primer dia.

## Abstract

This dissertation deals with security concerns regarding low-cost radio frequency identification (RFID) communications. RFID systems are composed by tags (also known as electronic labels) storing an identification sequence which can be wirelessly retrieved by an interrogator, and transmitted to the network through middlewares and information systems. Low-cost RFID integrates different technologies, regarding the resource constrained characteristic (thus, reduced cost) of the RFID tags.

The main example of low-cost RFID is the Electronic Product Code Class 1 Generation 2 (EPC Gen2) technology, which is designed to balance cost and functionality. The development of EPC Gen2 tags faces, in fact, several challenging constraints such as cost, compatibility regulations, power consumption, and performance requirements. As a consequence, the computational capabilities of EPC Gen2 tags are very simple. In this sense, the EPC Gen2 specification only considers two basic on board security features: pseudo-random number generators (PRNGs) and password-protected operations. The pseudo-randomness offered by on-board PRNGs is, indeed, used to protect the password-protected operations. PRNGs are also used as an anti-collision mechanism for inventorying processes, and to acknowledge other Gen2 specific operations (e.g., memory writing, decommission of tags, and self-destruction). PRNGs are, therefore, the crucial components that guarantee Gen2 security.

Cryptographic suitable PRNG designs must satisfy unpredictability characteristics. For example, an external adversary who eavesdrops the communication cannot compute the PRNG internal state, even if many outputs of the generator have been observed. The adversary cannot either compute the next sequence, even if many other previous sequences have been observed. If the adversary can observe, or even manipulate, the input samples that are fed by a PRNG, but its internal state is not known, the adversary must not be able to compute the next sequence. Finally, if the adversary has somehow learned the internal state of the PRNG, but the input samples that are fed in cannot be observed, then the adversary should not figure out the internal state of the PRNG after the re-keying operation. Most of these characteristics are, in fact, required by the EPC Gen2 specification. Hence, the use of weak PRNG designs that allow the predictability of the outgoing sequences introduces important security flaws in EPC Gen2 communications.

This dissertation includes the following points: In the first part, we present the main parameters of the EPC Gen2 technology, for both the communications interface and hardware characteristics. A complete state of the art on PRNGs and stream ciphers is introduced, with special emphasis to RFID and resource-constrained specific designs. The background obtained in this part gives us the framework to focus into the security analysis of RFID based on PRNGs.

The second part of the document deepens on the analysis of PRNGs for RFID. We demonstrate the likelihood to predict a novel PRNG proposal based on a linearity vulnerability, and we also demonstrate statistical deviations on PRNGs from commercial RFID tags. The work presented in this part implies a lack of security in the communications of RFID systems.

In the third part of this dissertation we propose a novel PRNG scheme for RFID, improving the state of the art for resource-constrained lowcost devices. Our proposal solves the linearity problem found in the analysis section, and is designed following the restrictions applying the low-cost RFID technology. A logical description and a hardware implementation are provided to test its suitability to the low-cost RFID technology.

Finally, the fourth and last part of this work presents an evaluation of our proposed PRNG based on four parameters: statistical behavior, security, hardware complexity and power consumption. The main interest is to demonstrate the hardware feasibility of our proposal to the EPC Gen2 technology, while providing a secure enough communication link.

The contribution of this dissertation is the improvement of the state of the art on security in RFID EPC Gen2 technology. With the knowledge obtained from the analysis of commercial EPC Gen2 tags, and the evaluation of scientific proposals, we have been able to propose a new PRNG design compatible with the hardware and statistical EPC Gen2 requirements, and with improved security properties. We can conclude that our work leads to new design paradigms and recommendations for the security in low-cost RFID, and particularly for the EPC Gen2 technology.

**Keywords**: Low-Cost RFID, EPC Gen2, PRNG, Lightweight Security, Attack Implementation, Empirical Analysis, Multiple Polynomial, Logical Gates, Power Consumption.

## Resum

El treball desenvolupat en aquesta tesi tracta la seguretat en sistemes d'identificació per radiofreqüència (RFID) de baix cost. Els sistemes RFID estan composats per tags (coneguts també com d'etiquetes electròniques) que emmagatzemen un codi d'identificació que es pot obtenir via radiofreqüència per un equip lector, i ser transmesa a la xarxa a través dels sistemes d'informació. L'RFID de baix cost integra diferents tecnologies amb un denominador comú, la limitació de recursos computacionals dels tags (és a dir el seu baix cost).

La tecnologia RFID de baix cost més comuna és l'Electronic Product Code Class 1 Generation 2 (EPC Gen2). El desenvolupament dels tags d'aquesta tecnologia ha de fer front a diverses limitacions, com són el cost de fabricació, compatibilitat amb les regulacions, consum de potència i funcionalitat. Com a conseqüència, les capacitats computacionals dels tags EPC Gen2 són limitades. En aquest sentit, les especificacions de la tecnologia EPC Gen2 només considera dos funcions de seguretat en els tags: generadors de nombres pseudoaleatoris (PRNGs) i operacions protegides amb contrasenya. La pseudoaleatorietat proporcionada als tags s'empra, de fet, per xifrar les operacions protegides amb contrasenva. Els PRNGs també són la base del mecanisme d'anticol·lisió en el procés d'inventariat dels tags, i del mecanisme de comprovació de recepció de certes operacions de l'estàndard EPC Gen2 (per exemple l'escriptura en memòria o la desactivació de tags). Per tant, els PRNGs són els elements bàsics en la seguretat de la tecnologia EPC Gen2.

Les sequències generades dels PRNG destinats a operacions criptogràfiques no poden ser predictibles. Per exemple, si un adversari escolta la comunicació no ha de ser capaç de calcular l'estat intern del PRNG, independentment del nombre de seqüències observades. L'adversari tampoc ha de ser capaç de predir la propera seqüència del generador, tot i que s'hagin escoltat les seqüències prèvies. Si l'adversari pot observar, o fins i tot manipular, les seqüències d'entrada al PRNG, però desconeix el seu estat intern, l'adversari no ha de poder predir la següent seqüència. Finalment, si l'adversari ha aconseguit conèixer l'estat intern del PRNG però no té accés a les seqüències d'origen, tampoc podrà calcular les noves seqüències del generador. EPC Gen2 inclou aquestes característiques a les seves especificacions. De fet, la utilització de dissenys de PRNG no adequats per criptografia que permetessin la predicció de les seqüències pseudoaleatòries generaria debilitats en les comunicacions de la tecnologia EPC Gen2.

El treball que recull aquesta tesi es resumeix a continuació: En la primera part, es presenten les principals característiques de la interfície de comunicacions i característiques de hardware de la tecnologia EPC Gen2. També s'inclou un estat de l'art de PRNG i sistemes de xifrat de flux, fent èmfasi en l'àrea dels RFID i dissenys amb recursos limitats. La informació d'aquesta primera part de la tesi proporciona el marc de coneixement per analitzar la seguretat en sistemes RFID basats en PRNGs.

La segona part d'aquest document es centra en l'anàlisi de PRNGs per RFID. Es demostra la possibilitat de predir les seqüències d'una proposta recent de PRNG per una vulnerabilitat deguda a la linealitat del disseny. També s'analitzen tags comercials, detectant desviacions estadístiques en els seus generadors pseudoaleatoris. Els resultats d'aquesta part de la tesi demostren una falta de seguretat en les comunicacions de la tecnologia RFID analitzada.

En la tercera part d'aquest document es proposa un nou disseny de PRNG per RFID, millorant l'estat de l'art per als dispositius de baix cost amb recursos limitats. Aquesta proposta resol els problemes de linealitat detectats prèviament, i en el seu disseny s'han considerat les restriccions inherents a la tecnologia RFID de baix cost. La proposta inclou una descripció lògica i una implementació en hardware per comprovar la seva aplicabilitat a la tecnologia RFID de baix cost. Finalment, la darrera part d'aquesta tesi presenta una avaluació de la proposta de disseny de PRNG, basada en els següents punts: propietats estadístiques, seguretat, complexitat de hardware i consum de potència. L'objectiu és demostrar l'adequació de la proposta de PRNG a les limitacions de la tecnologia EPC Gen2, proporcionant un nivell de seguretat suficient a les comunicacions.

La contribució d'aquesta tesi és la millora de l'estat de l'art en la seguretat per la tecnologia RFID EPC Gen2. Amb el coneixement obtingut de l'anàlisi de tags comercials, i l'avaluació de propostes de la literatura científica, es proposa un nou disseny de PRNG compatible amb els requisits de la tecnologia EPC Gen2, millorant-ne les propietats de seguretat. Es pot concloure que el treball inclòs en aquesta tesi condueix a un nou paradigma en el disseny i recomanacions per a la seguretat en sistemes RFID de baix cost, i en particular, per la tecnologia EPC Gen2.

**Paraules clau:** RFID de Baix Cost, EPC Gen2, PRNG, Seguretat Lleugera, Implementació d'Atac, Anàlisi Empírica, Múltiples Polinomis, Portes Lògiques, Consum de Potència.

# Acknowledgments

In the following lines I would like to thank those people which, somehow or other, have encouraged and helped me during the realization of this thesis.

En primer lloc, vull donar les gràcies al Dr. Jordi Herrera Joancomartí i al Dr. Joaquin Garcia Alfaro, directors d'aquesta tesi. Gràcies a la seva dedicació, energia i suport per introduir-me en el món de la recerca, i per fer possible aquesta tesi. A ambdós els vull expressar la meva més sincera gratitud. Així mateix, també vull agrair a la resta de membres del grup KISON tota l'ajuda rebuda en aquest període, així com a tot l'equip de l'IN3-UOC amb el seu programa de beques doctorals. Aquesta tesi ha sigut parcialment finançada pel Ministeri Espanyol d'Innovació i Ciència mitjançant els fons FEDER sota els projectes TSI2007-65406-C03-03 E-AEGIS, i CONSOLIDER CSD2007-00004 ARES.

En el desenvolupament d'aquesta tesi també hi tenen molt a veure els meus companys de doctorat de l'IN3, a tots ells gràcies pel fantàstic ambient de feina que he viscut aquests anys. També vull deixar constància del paper determinant que el Dr. Rafael Pous Andrés ha tingut al llarg dels meus períodes universitari i professional.

Des d'un vessant més personal, vull transmetre la meva sincera i profunda estimació a totes aquelles persones que des de Menorca, Barcelona o altres indrets, han compartit estones, i sentiments amb jo, com la meva família de Sant Just, que va acollir-me als primers anys universitaris com un més de la família, i a na Montse i en Manuel per l'atenció i afecte constant que m'han ofert en la tesi i fora d'ella. No vull deixar de pensar en els meus companys de pis, i tots els meus amics, aquesta tesi és també una mica seva.

Per acabar, aquesta tesi escrita entre Son Ganxo i Barcelona, no hauria estat possible sense els ànims i càlida confiança dels meus pares i la meva germana, els quals m'ho han donat tot, i són el model que he intentat seguir per arribar aquí. Aquesta tesi és una mica el reflex de la vostra constància i dedicació cap a jo. Finalment, he d'agrair de manera molt especial el recolzament i afecte constant de na Berta en aquest llarg viatge. Has viscut els moments bons i també dolents d'aquesta tesi, i de tots n'has sigut el far que ha il·luminat el bon camí. Per tot això i molt més, gràcies.

# Contents

| Co       | onter                                         | $\mathbf{nts}$                                              |                                                                                                                                                    |                  |                  | xv                                           |

|----------|-----------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------------------------------------|

| Lis      | st of                                         | Figur                                                       | es                                                                                                                                                 |                  |                  | xvii                                         |

| Lis      | st of                                         | Table                                                       | 5                                                                                                                                                  |                  |                  | xx                                           |

| Lis      | st of                                         | Acron                                                       | nyms                                                                                                                                               |                  | 2                | xxiii                                        |

| 1        | Intr<br>1.1<br>1.2<br>1.3                     | Main                                                        | ion<br>ation and Research Objectives<br>Contribution of the Dissertation<br>nent Organization                                                      |                  |                  | 4                                            |

| <b>2</b> | Stat                                          | te of A                                                     | rt                                                                                                                                                 |                  |                  | 9                                            |

|          | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | 2.1.1<br>2.1.2<br>Crypt<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | PC Gen2 Standard                                                                                                                                   | ·<br>·<br>·<br>· | ·<br>·<br>·<br>· | 12<br>18<br>22<br>23<br>24<br>25<br>31<br>34 |

|          | 2.4                                           | 2.3.2                                                       | LFSR-based PRNGs for low-cost RFID       .         Other low-cost RFID PRNGs       .         ation Tools       .         IAIK UHF Demo Tag       . | •                | •                | 41<br>44                                     |

|   |     | 2.4.2   | NIST Randomness Statistical Test Suite   | 48 |

|---|-----|---------|------------------------------------------|----|

|   | 2.5 | Chapt   | er Summary                               | 55 |

| 3 | Sec | urity A | Analysis for EPC Gen2 PRNGs              | 57 |

|   | 3.1 | Theor   | etical Attack to a PRNG EPC Proposal     | 58 |

|   |     | 3.1.1   | Analyzing the Che <i>et al.</i> Proposal | 59 |

|   |     | 3.1.2   | Exploiting Linearity Weaknesses          | 61 |

|   | 3.2 | Attac   | k Implementation                         | 67 |

|   |     | 3.2.1   | Che et al. Implementation and Setup      | 68 |

|   |     | 3.2.2   | Eavesdropping of PRNG Sequences          | 70 |

|   | 3.3 | Empir   | rical Analysis of Commercial ICs         | 74 |

|   |     | 3.3.1   | Experimental Setup                       | 75 |

|   |     | 3.3.2   | Commercial Analyzed ICs                  | 79 |

|   |     | 3.3.3   | Capture of Pseudo-random Sequences       | 83 |

|   |     | 3.3.4   | Reference Data                           | 84 |

|   |     | 3.3.5   | Statistical Evaluation                   | 86 |

|   |     | 3.3.6   | Analysis Conclusions                     | 93 |

|   | 3.4 | Chapt   | er Summary                               | 94 |

| 4 | Nev | v PRN   | IG Proposal                              | 97 |

|   | 4.1 | High I  | Level Description                        | 98 |

|   | 4.2 | Logica  | al Components                            | 01 |

|   |     | 4.2.1   | Internal PRNG Modules                    | 02 |

|   |     | 4.2.2   | System Parameters Summary 10             | 07 |

|   | 4.3 | Detail  | ed PRNG Execution                        | 08 |

|   | 4.4 | Hardv   | vare Specification                       | 12 |

|   |     | 4.4.1   | CMOS Technology                          | 13 |

|   |     | 4.4.2   | Logic Gates Equivalence                  | 16 |

|   |     | 4.4.3   | EPC Gen2 Compliant Implementation 1      | 16 |

|   |     | 4.4.4   | Hardware Specification Summary 12        | 27 |

|   | 4.5 | Chapt   | er Summary                               | 30 |

| <b>5</b>     | Eva   | luation of our PRNG Proposal                       | 133 |

|--------------|-------|----------------------------------------------------|-----|

|              | 5.1   | Statistical Properties                             | 134 |

|              |       | 5.1.1 Suitability to the Randomness Requirements . | 136 |

|              | 5.2   | Security Analysis                                  | 142 |

|              |       | 5.2.1 Description of Parameters                    | 142 |

|              |       | 5.2.2 Description of Attacks                       | 146 |

|              |       | 5.2.3 Security Summary                             | 153 |

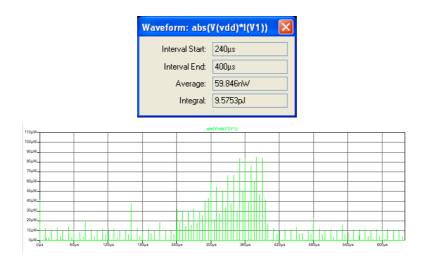

|              | 5.3   | PRNG Power Consumption                             | 154 |

|              |       | 5.3.1 Key Factors in Power Consumption             | 156 |

|              |       | 5.3.2 Power Consumption Evaluation                 | 160 |

|              | 5.4   | Chapter Summary                                    | 166 |

| 6            | Con   | clusions                                           | 169 |

|              | 6.1   | Concluding Remarks                                 | 169 |

|              | 6.2   | Results of this Dissertation                       |     |

|              | 6.3   | Future Research                                    | 173 |

| Bi           | bliog | raphy                                              | 174 |

| Publications |       |                                                    | 190 |

# List of Figures

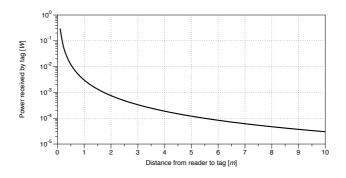

| 2.1  | Friis formula for power reception in FSPL                     | 12 |

|------|---------------------------------------------------------------|----|

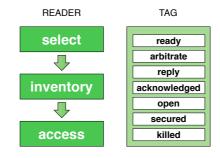

| 2.2  | Reader stages and tag states                                  | 14 |

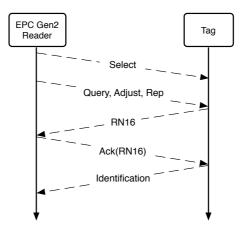

| 2.3  | Example of <i>Select</i> and <i>Inventory</i> process         | 15 |

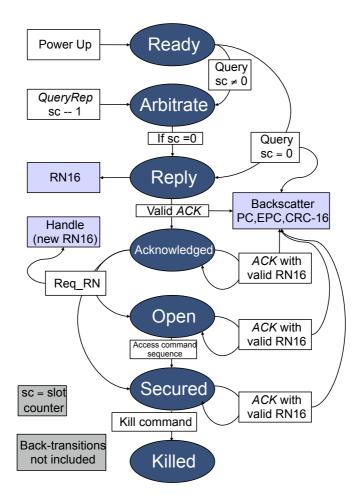

| 2.4  | EPC Gen2 tag state diagram                                    | 19 |

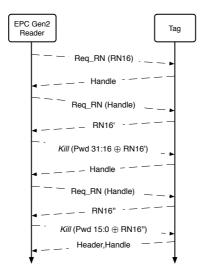

| 2.5  | EPC Gen2 kill command protocol                                | 21 |

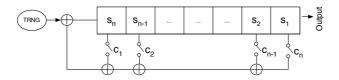

| 2.6  | Linear feedback shift register scheme                         | 29 |

| 2.7  | Working principle of stream cipher                            | 32 |

| 2.8  | Crypto1 stream cipher                                         | 37 |

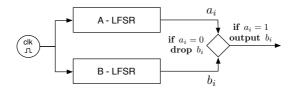

| 2.9  | The Shrinking Generator                                       | 39 |

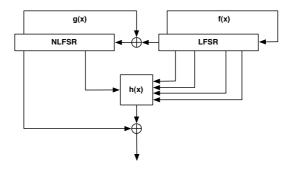

| 2.10 | The <i>Grain</i> Generator                                    | 40 |

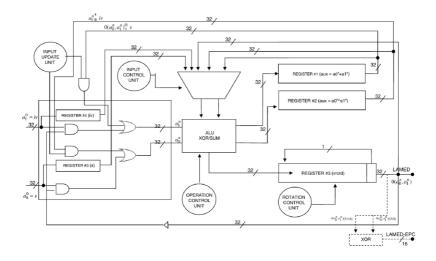

| 2.11 | LAMED PRNG for EPC Gen2 tags                                  | 44 |

|      | Image of UHF Demo Tag                                         | 46 |

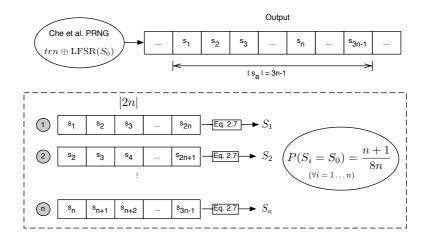

| 3.1  | PRNG scheme based on the Che et al. specifications.           | 59 |

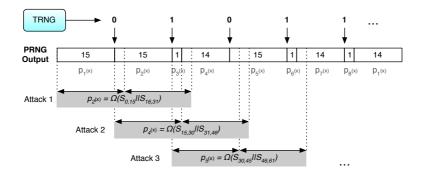

| 3.2  | Scheme of the attack to Che <i>et al.</i> PRNG                | 65 |

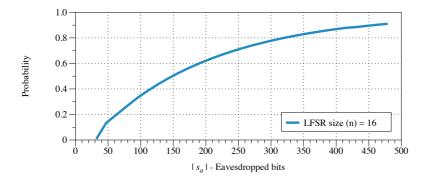

| 3.3  | Reliability on the Che <i>et al.</i> attack regarding $ s_a $ | 66 |

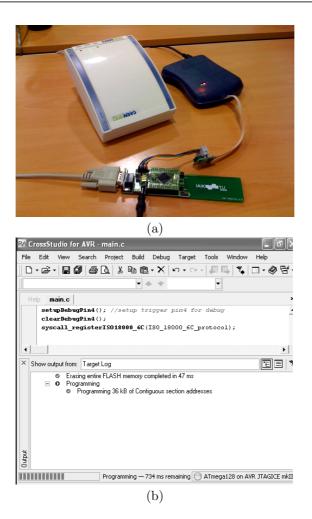

| 3.4  | RFID reader and Demo Tag experimental setup                   | 69 |

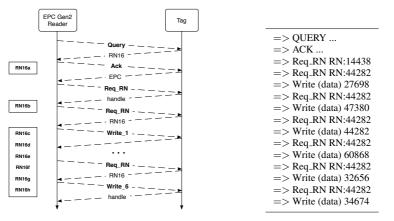

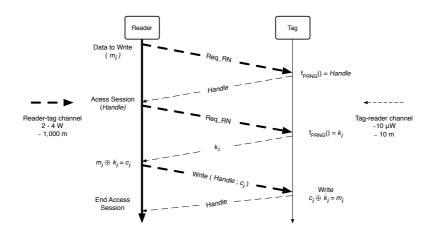

| 3.5  | Write process for EPC Gen2 and the PRNG utilization           | 71 |

| 3.6  | Che et al. PRNG attack for real Gen2 environment.             | 73 |

| 3.7  | Commercial ICs RN16s extraction method setup                  | 77 |

| 3.8  | Extraction method (software) screen captures                  | 78 |

| 3.9  | Sample tags using the analyzed ICs                            | 81 |

| 3.10 | Commercial ICs PRNGs ratios                                   | 84 |

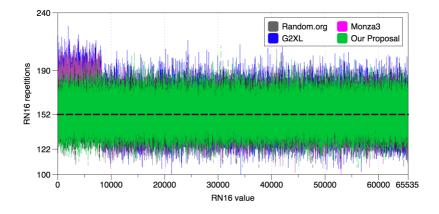

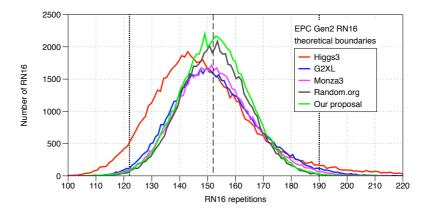

| 3.11 | Frequency analysis for individual RN16 values                 | 91 |

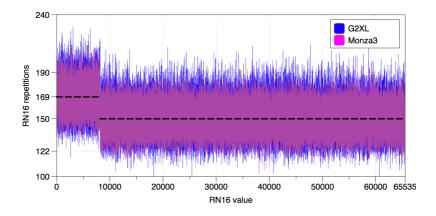

|      | $G2XL$ and $Monza \ 3 \ RN16$ frequency analysis              | 92 |

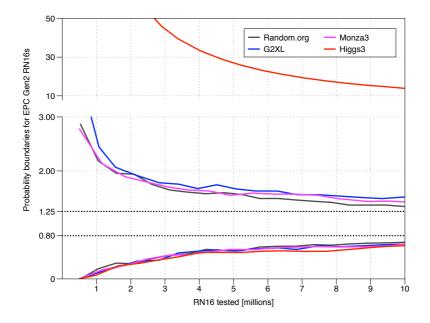

|      | Commercial ICs RN16s $P_{max}$ and $P_{min}$ analysis         | 94 |

|      |                                                               |    |

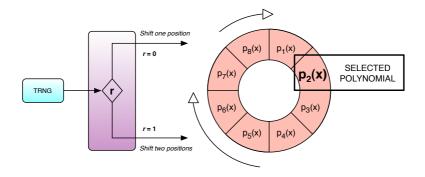

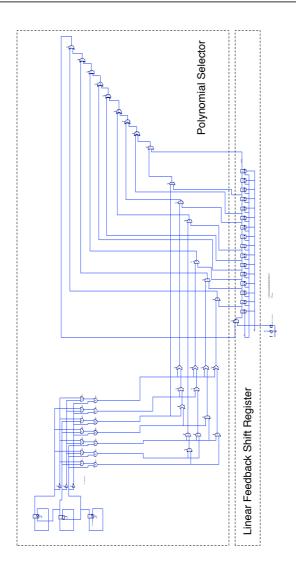

| 4.2  | Polynomial Selector function                                          | 101 |

|------|-----------------------------------------------------------------------|-----|

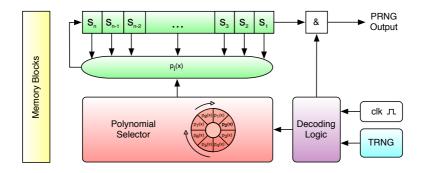

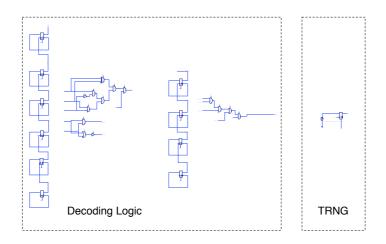

| 4.3  | Block diagram of our PRNG proposal                                    | 102 |

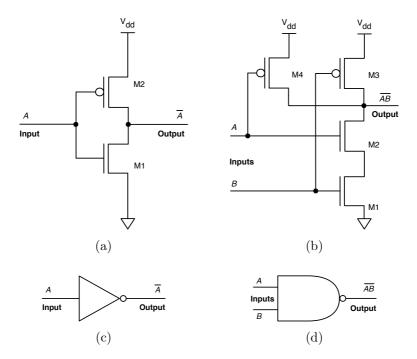

| 4.4  | INV and NAND logic gates                                              | 114 |

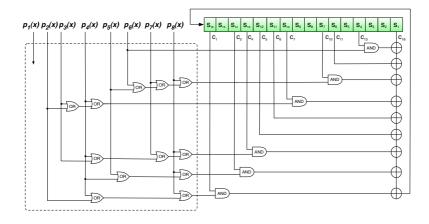

| 4.5  | Multiple Polynomial selector                                          | 119 |

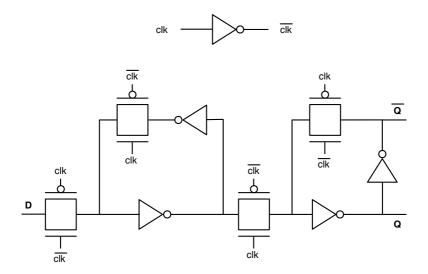

| 4.6  | D-flip flop implementation with 4.5 GE                                | 120 |

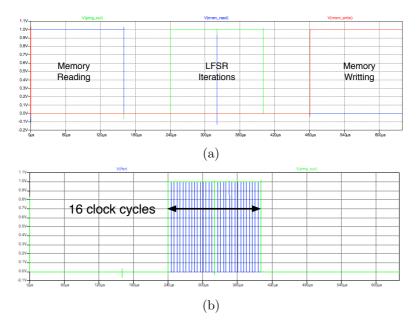

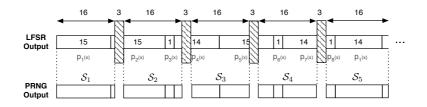

| 4.7  | PRNG time slots scheme                                                | 131 |

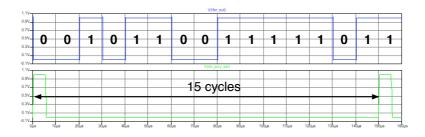

| 4.8  | Pseudo-random sequence transmission example 1                         | 131 |

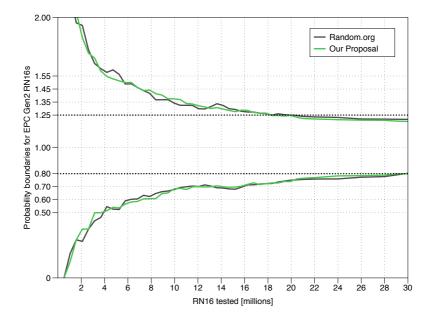

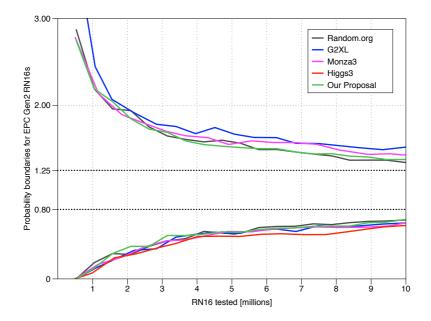

| 5.1  | PRNG proposal EPC Gen2 compliance                                     | 138 |

| 5.2  | PRNG proposal $P_{max}$ and $P_{min}$ behavior $\ldots \ldots \ldots$ | 139 |

| 5.3  | Frequency analysis of RN16s for our PRNG proposal . 1                 | 140 |

| 5.4  | Frequency distribution for our PRNG proposal 1                        | 140 |

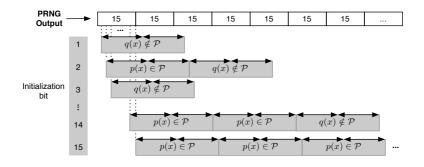

| 5.5  | Attack synchronization step                                           | 148 |

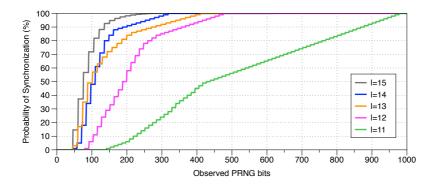

| 5.6  | Attack synchronization step probability 1                             | 149 |

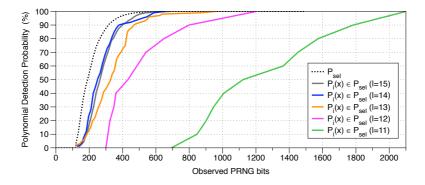

| 5.7  | Polynomial detection step                                             | 150 |

| 5.8  | Attack detection step probability                                     | 152 |

| 5.9  | Polynomial detection with 3 discarded bits 1                          | 153 |

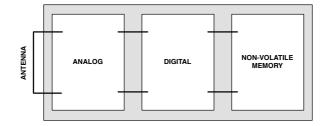

| 5.10 | Layout of a RFID tag                                                  | 155 |

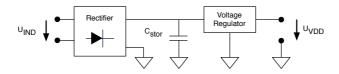

| 5.11 | Power supply of passive RFID tags                                     | 158 |

| 5.12 | Hardware design of LFSR and Polynomial Selector 1                     | 163 |

|      | 0 0                                                                   | 164 |

| 5.14 | Spice power consumption simulation                                    | 165 |

# List of Tables

| 2.1  | EPC Gen2 tags main properties                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | EPC Gen2 tag's memory logic map                                                                                                                              |

| 3.1  | Che et al. PRNG NIST test results 62                                                                                                                         |

| 3.2  | Attack success rate for $ s_a  = 3n - 1. \dots 66$                                                                                                           |

| 3.3  | Value of $ s_a $ for a successful attack                                                                                                                     |

| 3.4  | RN16s involved in EPC Gen2 operations 71                                                                                                                     |

| 3.5  | Commercial ICs main parameters                                                                                                                               |

| 3.6  | Resume of ICs PRNG properties                                                                                                                                |

| 3.7  | Commercial EPC Gen2 PRNGs NIST test results 87                                                                                                               |

| 3.8  | Frequency (Monobit) test results                                                                                                                             |

| 4.1  | Design parameters summary                                                                                                                                    |

| 4.2  | Example of feedback polynomials $(n = 16) \dots \dots$ |

| 4.3  | LFSR iteration example $(r = 0)$                                                                                                                             |

| 4.4  | LFSR iteration example $(r = 1) \dots $                |

| 4.5  | Logic GE based on static CMOS designs                                                                                                                        |

| 4.6  | Primitive polynomials matrix representation 121                                                                                                              |

| 4.7  | Multiple Polynomial hardware implementation 123                                                                                                              |

| 4.8  | Polynomial combination parameters                                                                                                                            |

| 4.9  | Logical GE count for our proposed PRNG 128                                                                                                                   |

| 4.10 | GE comparison of lightweight PRNG proposals $\ . \ . \ . \ 129$                                                                                              |

| 5.1  | NIST statistical test suite results                                                                                                                          |

| 5.2  | EPC Gen2 second randomness property test 141                                                                                                                 |

| 5.3  | EPC Gen2 third randomness property test 141                                                                                                                  |

| 5.4  | Definition of parameters for security analysis 144                                                                                                           |

|      |                                                                                                                                                              |

## List of Acronyms

**ASK** Amplitude-Shift Keying

${\bf DB}\,$  Data Base

**CMOS** Complementary Metal-Oxide Semiconductor

**CRC** Cyclic Redundancy Code

**DoS** Denial of Service

**EEPROM** Electrically Erasable Programmable Read-Only Memory

${\bf EPC} \ {\rm Electronic} \ {\rm Product} \ {\rm Code}$

**ETSI** European Telecommunications Standards Institute

**FF** Flip-flop

**FPGA** Field-Programmable Gate Array

**FSPL** Free-Space Path Loss

**GE** Gate Equivalent

Gen2 Generation 2

**HF** High Frequency

**IC** Integrated Circuit

xxiii

- $\ensuremath{\mathsf{IEC}}$  International Electrotechnical Commission

- **ITF** Interrogator Talks First

- **ISO** International Organization for Standardization

- **ISP** In-System Programming

- JTAG Joint Test Action Group

${\sf LCG}$  Lineal Congruential Generator

- **LFSR** Linear Feedback Shift Register

- **LSB** Less Significant Bit

- MHz Mega Hertzs

- **MOSFET** Metal-Oxide Semiconductor Field-Effect Transistor

- **MSB** Most Significant Bit

- **NIST** National Institute for Standards and Technology

- ${\sf NVM}$  Non-Volatile Memory

- **PC** Protocol Control

- **PCB** Printed Circuit Board

- **PRNG** Pseudo Random Number Generator

- **PSK** Phase-Shift Keying

- **QoS** Quality of Service

- **RFID** Radio Frequency Identification

- RN16 16-bit Random Number

- ${\sf RNG}\,$  Random Number Generator

- ${\bf ROM}\ {\rm Read-Only}\ {\rm Memory}\ {}$

- **RS-232** Recommended Standard 232

- **SPICE** Simulation Program with Integrated Circuit Emphasis

- **UART** Universal Asynchronous Receiver / Transmitter

- ${\sf UHF}\,$ Ultra High Frequency

- ${\bf USB}\,$  Universal Serial Bus

- **VLSI** Very Large-Scale-Integration

- **XOR** Exclusive OR

1

## Introduction

Radio Frequency Identification (RFID) technology is an automatic identification method for retrieving digital information without physical contact or line-of-sight, that is revolutionizing the manner in which objects and people can be identified by computers [16]. Tagging objects or even people with smart labels (the so called RFID tags) emitting identifying information in form of binary modulated signal, is the way computers can actually understand the presence of objects. RFID technology is the closest approach to the ubiquitous computing [84] or the future *Internet of Things*.

RFID labels are frequently referred as the next generation barcodes. Although the utility is the same (the identification of an object), RFID offers two main advantages over conventional barcode systems. On the one hand, optical barcodes only indicates the generic product, whereas a RFID tag can identify the item (being able to distinguish different objects from the same product). On the other hand, there is no need of line-of-sight. Thus, while optical barcodes must be identified one by one, RFID tags can be read much faster, without human intervention and in large quantities [16, 48].

The unassisted wireless identification makes the RFID very attractive in areas like product traceability, inventorying or personal identification, but it also creates setbacks. Like the rest of wireless information technologies, RFID information transferred between sender and receiver is not completely secure. The air interface is much more insecure than the wired one, because the only presence of an attacker in the communication area gives him the opportunity to obtain information in a malicious way. The scarce available energy on tags, and tag computational capabilities are also determinant for security in RFID.

In addition, RFID is very related with personal identification. Let us imagine a postal user sending a RFID enabled letter, with some easy techniques. It will not be difficult to link sender and receiver by eavesdropping the letter identification. Privacy issues must, therefore, also be considered.

#### 1.1 Motivation and Research Objectives

This research dissertation is focused in low-cost passive RFID. This is the case of the Electronic Product Code Class 1 Generation 2 (EPC Gen2) [25] for UHF, designed by EPCglobal [26] and developed in the MIT Auto-ID labs. This technology is being widespread in the retail industry [64], and also other sectors [78], thanks to the reduced price of their tags. EPC Gen2 was designed giving priority to reduce the price by means of a very simple performance [48]. Indeed, the price is the main reason for the industry to adopt or to refuse a technology. It is not a coincidence that EPC technology appearance coincided with the explosion of RFID adoption in the retail industry [86], because tag price should not increase the product cost [48]. It can be said that a small area chip (thus a few logical gates) and no battery on-board (thus using radio frequency waves to energize the tag) will be a cheap tag. But that also means that there is almost no place for additional capabilities in the chip like security mechanisms. In fact, security measures implemented on those devices are scarce and are basically reduced to the use of Pseudo-Random Number Generators (PRNG) and small passwords [16].

Providing security for RFID systems is not a simple task. Established approaches for protecting communications cannot be applied without modification of the specific protocols because of the special characteristics of RFID systems [29]. The singularity of RFID systems lies in the properties of communication, which makes the communication channel (the air-interface) very susceptible to security threats. Specially for EPC Gen2 systems due to its simplicity and specific differences in the link's properties (forward and backward channel).

Additionally, in the low-cost RFID there is a big difference in the computing capabilities of readers and tags, what makes the implementation of security protocols challenging. Computation of cryptographic primitives is generally much more computationally expensive compared to the simple tasks of a simple tag. Hence, security measures have to be designed considering the special requirements of RFID systems into account. These low-cost tags are expected to be deployed on a large scale. Hence, there is a potential danger of obtaining sensible information from the tags. For example an adversary can link a specific tag identification with the price of the object, thus, prioritize actions regarding the economic target. Furthermore, pri-

vate information about people can be obtained by stealthily scanning the tags that they carry [16].

We focus our research in PRNGs as main security tool for low-cost RFID. The use of weak PRNGs that allow the predictability of the outgoing sequences introduce important security flaws in any communication system. For example, it might allow an adversary to bypass the security of the password-protected commands defined in the EPC Gen2 standard (e.g., the *access* and the *kill* commands). This is indeed possible if the on board tag's PRNG is predictable, e.g. due to its bad statistical properties, since it then suffices to apply a simple XOR operation with the predicted sequences and the contents of the messages transmitted over the reader-to-tag channel to decrypt the remainder ciphertext (e.g., the protected password values).

Our motivation is to improve the security state-of-the-art in low-cost passive RFID by the analysis and improvement of pseudo-random number generators. PRNGs are necessary in the current version of the most extended low-cost RFID technology: the EPC Gen2 Standard. But PRNG can also be used as a core elements for future cryptographic primitives implementation on RFID tags. Thus cryptographically secure PRNGs are necessary for the current and future technology. Our goal is to design a suitable PRNG to be adaptable to the possibilities of the technology, offering the secure behavior while not exceeding the low-cost requirements.

#### 1.2 Main Contribution of the Dissertation

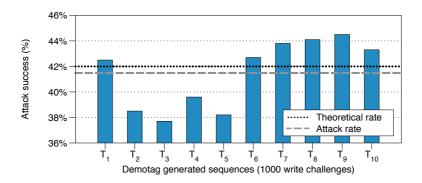

To summarize, the main contributions of this dissertation can be concentrated in four main points: Attack to EPC Gen2 PRNG proposal: We have demonstrated the vulnerability of the EPC Gen2 PRNG proposed by Che *et al.* [18]. The vulnerability is related to the inherent linearity of linear feedback shift registers, which is translated into a predictability threat. The Che *et al.* scheme is theoretically predictable after only 128 bits with a confidence of 42%, as demonstrated in [60]. The attack was proved to be implementable in EPC Gen2 compatible devices, using a novel method for eavesdropping pseudo-random sequences from EPC Gen2 tags presented in [59].

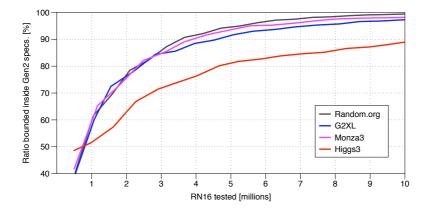

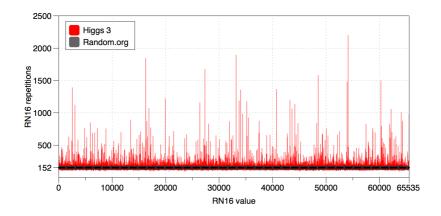

Analysis of EPC Gen2 commercial PRNGs: Additionally to the study of proposals in the scientific literature, we have analyzed the pseudo-random sequences generated by ICs attached to commercial tags. Using statistical testing, we have found evidences of non-randomness in the analyzed sequences. Furthermore, we propose a different approach to measure the sequences' randomness quality, based on the frequency of the sequences regarding the size of the dataset.

**New PRNG proposal based on multiple-polynomial:** We have proposed a new PRNG design based on a linear feedback shift register (LFSR) for security applications, compliant with the EPC Gen2 technology. Our proposal handles the LFSRs inherent linearity with the multiple-polynomial architecture, being the first time it is used for security applications. The PRNG proposal has been described at a logical level and also following a hardware scheme using registers, logic gates and non-volatile memory. Due to the severe power and area restrictions in the EPC Gen2 tags, an evaluation of primitive polynomials of degree 16 with suitable characteristics for its hardware implementation, is also presented in this dissertation. A preliminary version of the proposal was presented in [31].

**Evaluation of our PRNG proposal based on EPC Gen2 requirements:** Based on our PRNG proposal, a complete evaluation has been performed. Regarding that our PRNG is intended to work as a cryptographic tool in a resource-restricted device, the aim of this evaluation is to demonstrate the suitability of our proposal to the EPC Gen2 technology. The evaluation includes statistical and formal security analysis, hardware complexity (area) regarding similar proposals presented in the literature, the power consumption of the tag's digital scheme based on a SPICE simulation, and finally a time execution evaluation.

#### **1.3** Document Organization

The rest of this dissertation is organized as follows:

Chapter 2 is focused in the EPC Gen2 technology characteristics, specially focused on the EPC Gen2 tags on-board main security tool: the PRNG. Furthermore, different security mechanisms based on stream ciphers for constrained devices are introduced, as well as scientific proposals for PRNGs designed for low-cost RFID. We also review the evaluation tools used in this dissertation, including a testing device prototype and statistical evaluation tests.

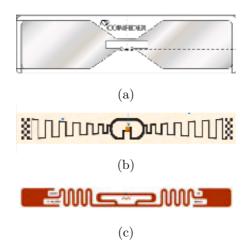

Chapter 3 presents a practical implementation attack on a weak PRNG designed specifically for EPC Gen2 tags. We demonstrate that it is feasible to eavesdrop a small amount of pseudo-random values by using standard EPC commands and using them to determine the PRNG configuration that allows to predict the complete output sequence in a theoretical way, and performing a real attack with EPC Gen2 compatible devices. Also in this chapter, we present an analysis of the pseudo-random sequences generated from real commercial tag integrated circuits (ICs). Specifically, ICs from vendors such as *NXP*, *Alien* and *Impinj* are tested. The main analyzed parameter is the probability of appearance of any single 16-bit pseudo-random sequence, evaluating the statistical properties of the commercial ICs PRNG.

Chapter 4 proposes a new pseudo-random number generator design for EPC Gen2. This generator is based on a 16-bit linear feedback shift register with multiple feedback primitive polynomials fed by a physical source of randomness. The proposed PRNG successfully handles the inherent linearity of linear feedback shift register based PRNGs and satisfies the hardware requirements imposed by the UHF RFID technology. This chapter includes a high level logical description of the method used to obtain the randomness on the tag, and a preliminary hardware specification implementing the designed technique.

Chapter 5 evaluates the suitability of our design to the specifications required for the EPC Gen2 standard for RFID. Statistical analysis of the pseudo-random sequences from our generator confirms the validity of the proposed technique. Furthermore, a formal security analysis is presented, evaluating the PRNG security using attack scenarios with different capabilities. Regarding the PRNG power consumption, an electronic circuit simulation of the proposed hardware is presented, as well as an execution time analysis evaluation according to the current technology implementing EPC tags.

Finally, concluding remarks and a discussion about the possible future research directions to follow are given in Chapter 6.

# 2

#### State of Art

Low-cost radio frequency identification (RFID) tags are becoming a successful technology to increase the efficiency and productivity in the logistics sector. As the costs of tags are dropping, logistics departments are taking more attention to the possibility to integrate this real-time technology in the business processes in order to improve the visibility and accuracy of the logistic operations [64].

The deployment of the RFID technology is becoming more important thanks to the standardization process through the Electronic Product Code (EPC) Class 1 Generation 2 (hereinafter denoted as Gen2) tag standard [25] promoted by EPCglobal. EPCglobal standardization covers the whole RFID architecture, from tag data structure to network communication specifications. EPC tags are not provided with on-board batteries, but are passively powered through radiofrequency waves. The remainder of this chapter is organized as follows: Section 2.1 introduces the EPC Gen2 technology characteristics, specially focused on the EPC Gen2 tags on-board main security tool: the *pseudorandom number generator* (PRNG). Section 2.2 introduces different security mechanisms based on stream ciphers for constrained devices, and Section 2.3 overviews scientific proposals for PRNGs designed for low-cost RFID. Finally, Section 2.4 introduces the evaluation tools used in this dissertation, including a testing device prototype and statistical evaluation tests.

#### 2.1 The EPC Gen2 Standard

The EPC technology is based on the use of RFID. This technology is intended to be the successor of the nowadays ubiquitous barcodes. Designed in the Massachusetts Institute of Technology Auto-ID Labs, and developed by the EPCGlobal consortium [26], the EPC technology represents the key component of an architecture known as EPCglobal Network [25]. The main components of the RFID system are the electronic labels or tags, the readers and the Information Systems (IS) e.g middlewares, databases and servers. The main goal of this architecture is the object-in-motion automatic identification in the supply chain and factory production.

The EPC tags (cf. Table 2.1) are passive devices powered by the electronic field generated by the reader, due to the absence of onboard batteries. They work worldwide on the ultra high frequency (UHF) band between 860 and 960 MHz, depending on the RF regulations for each continent. The communication range between tags and readers depends on the electric field, thus, it may vary depending on the power supply and antenna design, but also on the kind of surface where the tag is placed. RFID tags are intended to be deployed widely so they must be cheap. EPC Gen2 Tags are composed by two main elements, the *Integrated Circuit* (IC) and the *antenna*. The IC is based on a state machine model and processes and stores the RFID information. The antenna is intended to receive and transmit RFID signals, and also to energize the IC. In a low-cost RFID system, like EPC Gen2, the tags are very simple and resource limited, allowing to reduce their cost under the 10 cents of US dollar [89]. This reduction on the tag cost is proportional to the size of the silicon IC. The typical measure of space in silicon ICs is the *gate equivalent* (GE) that is equivalent to a boolean *two-input NAND gate*. The estimations on available GE for EPC Gen2 implementations are around 10,000 GE [85].

The EPC Gen2 system communication model is common to other low-cost RFID systems where the interrogator (reader) talks first (ITF). EPC Gen2 tags are passive and power dependent from the reader to respond the queries. The communication between tag and reader in the EPC Gen2 system is organized in three stages. In the *Selection* and *Inventorying* stages, the reader initiates the communi-

| Identification             | 96 bit                  |

|----------------------------|-------------------------|

| Communication range        | $\sim$ 5 m              |

| Tag power consumption      | $\sim$ 10 $\mu {\rm W}$ |

| Frequency (Europe)         | 865-868 MHz (UHF)       |

| Tags Tx ratio              | $40$ - $640~{\rm kbps}$ |

| Tags Rx ratio              | 26.7 - 128 kbps         |

| Identifications per second | $\sim 200$              |

Table 2.1: EPC Gen2 tags main properties

Figure 2.1: At five meters an EPC Gen2 tag receives around 100  $\mu W$  from the reader

cation sending identification queries. The available tags in the communication range respond with a 16-bit provisional identifier (hereinafter denoted as RN16) extracted from the implemented PRNG on-board. When the reader acknowledges the provisional identifier, each single tag sends an identification sequence. The EPC Gen2 standard defines the identification sequence with 96 bits [25], but other identification sizes can be used depending on the tag manufacturer. If the reader manages to access or modify the tag memory content at this point, the *Access* stage is started. In the remainder of this section we introduce the main properties of the EPC Gen2 technology used in this dissertation.

# 2.1.1 Main Properties

EPC Gen2 tags do not have a power source. Instead, tags are passively powered following an ITF protocol, thus, tags can only respond after a message is sent by the reader. Regarding the physical layer, the reader powers up the tag by transmitting a radio frequency (RF) continuous wave to the tag, and the tag backscatters a signal to the reader using the modulation of the reflection coefficient of its antenna. RFID passive tags are powered through the electromagnetic waves received from the interrogator. Only a small fraction of the power emitted by the interrogator is received by the RFID tag antenna, inducing a voltage to the RFID tag IC. The European Telecommunications Standards Institute (ETSI) [45] regulates the RF spectrum for the European region. It allows for the RFID UHF communication a maximum transmission power of 2 W from EPC Gen2 readers. According to the *Friis transmission equation* (cf. Equation 2.1) [79], the signal power received by a RFID tag IC depends on the power signal from the reader, the gain of the antennas of both tag and reader and the inverse of the free-space path loss (FSPL) equation.

$$P_{RX,tag} = P_{TX,reader}G_{reader}G_{tag}\left(\frac{\lambda}{4\pi d}\right)^2 \tag{2.1}$$

The FSPL for the UHF frequency, which in the equation is represented by its wavelength  $(\lambda)$ , decline quadratically (order of magnitude) with the distance (d) to the interrogator antenna. The communication distance d for the RFID tags depends on the factors included in the Equation 2.1 and it is usually considered of about 5 meters, that is, the maximum distance where the signal power is sufficient to activate the tag IC. Figure 2.1 shows the approximated tag received power curve depending on the distance between reader and tag. This distance is considered in ideal conditions but on real RF environments there are mitigation factors reducing such distance. Signal reflection, absorbing materials or inadequate antenna orientation are possible factors for reducing the communication distance. The communication is half-duplex thus, simultaneous transmission and reception is not allowed.

Figure 2.2: Reader stages and tag states for the EPC Gen2 protocol

The communication stages in the EPC Gen2 protocol are organized in three stages (cf. Figure 2.2):

- Select: In this stage, the reader selects a subset of the tag population in the communication range for inventory and access using one or more *Select* commands.

- Inventory: The process by which a reader identifies tags. An inventory round is initialized by the reader sending *Query* commands. One or more tags may reply, thus, the tags use an anti-collision protocol to avoid collisions. After *selection* the tag loads a random slot counter between *zero* and  $2^Q 1$  (with  $0 \le Q \le 15$ , automatically adjusted or user-defined) decreasing one unit for each *Query* command reception. When the counter reaches the value *zero*, the tag initiates the reply. If the reader detects a single tag reply, it requests the identification from the tag. Figure 2.3 shows an example of a reader inventorying a single tag.

Figure 2.3: Example of *Select* and *Inventory* process

• Access: The process by which a reader modifies or reads individual tags' memory areas. This stage can only be initiated after a successful inventory process.

The tag memory is logically divided into four banks (cf. Table 2.2):

- **Reserved**: This memory block shall contain the 32-bit access and kill passwords. If these passwords are not specified, a logic *zero* is stored on that memory area. Tags with a *non zero* access password have to receive that value before transitioning to a secure state.

- **EPC**: This block contains the Protocol Control (PC) bits and the 96-bit identification code (denoted as EPC) that identifies the tag. This memory block also contain a CRC-16 (defined in ISO/IEC 13,239) checksum of the PC and EPC codes.

- **TID**: This area of memory shall contains an 8-bit ISO/IEC 15,693 class identifier. Moreover, sufficient information to identify the custom commands and optional features supported by the tag is also specified in this memory block.

- User: This memory block is not mandatory thus, the block size is not specified in the standard. Instead, the User memory is factory-configured depending on the manufacturer.

The communication between reader and tags in the EPC Gen2 protocol is organized in identification stages and tag states. The following paragraphs describe each of the possible tag states (cf. Figure 2.4):

| User:     | Optional                |

|-----------|-------------------------|

| TID:      | TID [15:0]              |

|           | TID [31:16]             |

| EPC:      | XPC_W1 [15:0]           |

|           | EPC [15:0]              |

|           | :                       |

|           | EPC [95:79]             |

|           | PC [15:0]               |

|           | CRC [15:0]              |

| Reserved: | Access Password [15:0]  |

|           | Access Password [31:16] |

|           | Kill Password [15:0]    |

|           | Kill Password [31:16]   |

Table 2.2: EPC Gen2 tag's memory logic map

- **Ready**: After being energized, a tag that is not killed enters in the *ready* state. The tag shall remain in this *ready* state until it receives a *Query* command. Tag loads a Q-bit number from its PRNG, and transitions to the *arbitrate* state if the number is *non-zero*, or to the *reply* state if the number is *zero*.

- Arbitrate: A tag in an *arbitrate* state shall decrement its slot counter every time it receives a *QueryRep*, transitioning to the *reply* state and backscattering a RN16 when its slot counter reaches *zero*.

- **Reply**: A tag shall backscatter a RN16, once entering in *reply* state.

- Acknowledged: If a tag in the *reply* state receives a valid acknowledge (*Ack*), it shall transition to *acknowledge* state, backscattering its PC, EPC, and CRC-16. Otherwise, the tag returns to the *arbitrate* state.

- **Open**: After receiving a *Req\_RN* command, a tag in *acknowl-edge* state whose access password is *non-zero* shall transition to *open* state. The tag backscatters a new RN16 that both reader and tag shall use in subsequent messages. Tags in an *open* state can execute all access commands except *Lock* and may transition to any state except *acknowledge*.

- Secured: A tag in *acknowledge* state, which access password is *zero*, shall transition to *secured* state, upon receiving a *Req\_RN* command. The tag backscatters a new RN16 that both reader and tag shall use in future messages. A tag in the *open* state, which access password is *non-zero*, shall transition to a *secured* state, after receiving a valid access command, which includes the same *handle* that was previously backscattered when it

transitioned from *acknowledge* state to the *open* state. Tags in *secured* state can execute all access commands and may transition to any state except *open* or *acknowledge*.

• Killed: Once a *kill* password is received by a tag in either *open* state or *secured* state, it shall enter the *killed* state. *Kill* permanently disables a tag. A tag shall notify the reader that the killed operation was successful, and shall not respond to any reader thereafter.

# 2.1.2 Security in the EPC Gen2 Standard

As in many other emerging technologies, attacks against different services of the EPC architecture may expose its users to security risks and privacy violations. Indeed, if countermeasures are not handled properly at the lowest level of the architecture, where the exchange of information between Gen2 tags and readers is carried via insecure wireless connections, attacks such as data disclosure, cloning, impersonation, and denial of service may succeed. However, the development of Gen2 security countermeasures faces several challenging constraints such as cost, compatibility regulations, power consumption, and performance requirements. From the approximately 10,000 available GE in EPC Gen2 ICs only 2,000 to 5,000 can be devoted to security tasks [85]. Thus, on-board security tools must be necessarily simple.

The EPC Gen2 communication protocol includes basic security mechanisms for the *Access* stage in the tags. The EPC Gen2 standard includes in its specification a 32-bit password to protect the tag memory access. Moreover, the standard includes a 32-bit password for the *kill*

Figure 2.4: EPC Gen2 tag state diagram extracted from [25]

command execution. This command allows to permanently deactivate the tag performance (kill), or to unblock specific tag memory areas previously blocked (*recomission*), depending on the command

codification [25]. The kill and access passwords are stored in the tag reserved memory area (Table 2.2 describes the EPC Gen2 tags different memory areas).

To avoid revealing sensible information in the *reader-to-tag* channel (e.g. passwords or new identifiers) susceptible to be eavesdropped from a non authorized reader, the EPC Gen2 tags include a PRNG to encrypt the transmitted information on that channel. Hence, when the EPC reader requests the *Access* to a tag, the tag sends 16-bit nonces in plaintext to encrypt the content to be sent by the reader, by means of a bitwise exclusive OR (XOR) operation.

To execute the kill command to an EPC Gen2 tag for example, the reader shall previously identify it. Once the tag has sent the 96-bit identification, the reader switches to the *Access* stage (cf. Figure 2.5). To successfully switch to the *Access* stage the reader requests a 16-bit nonce to the tag to be used as a session key for the *Access* stage. When the tag provides the RN16 (represented as *Handle*), the reader requests a new nonce (RN16') to start the *kill* password encryption. This process is repeated for the two halves of the kill password (Pwd [31:16] and Pwd [15:0]) with a new RN16" key. To confirm the operation success the tag sends a last message containing a header and the *Handle* code.

## Security paradigm

Traditional keystream generators share a secret k as a key for the PRNG *one-time pad* communication between *sender* and *receiver*. The use of deterministic PRNGs to generate exactly the same sequence in both sender and receiver sides is commonly used.

Figure 2.5: EPC Gen2 kill command protocol

However, the specific communication model of EPC Gen2 systems uses another paradigm in which *sender* and *receiver* cannot share any secret k. Instead, the low-power tag-to-reader communication is used to transmit in plaintext the nonces to be used as a keystream for the reader-to-tag communication. The next paragraphs detail the keystream generator characteristics of the EPC Gen2 technology.

## **On-board PRNG**

Existing commercial EPC Gen2 tags implement an on-board PRNG, as required by the EPC specifications [25]. However, companies are reluctant to provide their designs [75]. Manufacturers simply refer to testbeds that show the accomplishment of some compatibility requirements. They fail to offer convincing information about the security

of their designs. This is mostly security through obscurity, which is always ineffective in security engineering, as it has been shown with the disclosure of the PRNG used in the MIFARE Classic chip [30] that has shown a vulnerable PRNG.

The on-board PRNG generates 16-bit pseudo-random sequences, and shall have the ability to provide RN16s to the Q anti-collision system, to acknowledge other Gen2 specific operations (e.g., memory writing, decommission of tags, and self-destruction), and as a source for the *one-time-pad* based *cover-coding* ciphering system for the access stage of the tag identification. PRNGs are, therefore, the crucial components that guarantee Gen2 security. As specified in the standard the PRNG is supposed to meet the following randomness criteria:

- 1. The probability that any single 16-bit sequence j drawn from the generator shall be bounded by  $\frac{0.8}{2^{16}} < Prob(j) < \frac{1.25}{2^{16}}$ .

- 2. Among a tag population of up to ten thousand tags, the probability that any two tags simultaneously generate the same 16-bit sequence shall be less than 0.1%.

- 3. The chance of guessing the next 16-bit sequence generated by a tag shall be less than 0.025% even if all previous outputs are known to an adversary.

# 2.2 Symmetric Cryptography Based on Stream Ciphers

In this section, we introduce an overview of cryptographic primitives with suitable characteristics for its implementation on RFID devices. Section 2.3 introduces specific security proposals built from the cryptographic primitives shown in this section.

# 2.2.1 Cryptography Goals

Cryptography is the study of mathematical techniques related to aspects of information security such as confidentiality, data integrity, entity authentication, and data origin authentication. The application of cryptographic primitives in information systems is based on the following goals [61]:

- *Confidentiality* is used to keep information accessible only to the authorized entities. Secrecy is a term synonymous with confidentiality and privacy. There are numerous approaches to provide confidentiality, from physical protection to mathematical algorithms which render data unintelligible.

- *Data integrity* addresses the unauthorized alteration of data. To assure data integrity, one must have the ability to detect data manipulation by unauthorized parties. Data manipulation includes insertion, deletion, and substitution.

- Authentication is closely related to identification. This function applies to both entities and information itself. Two parties entering into a communication should identify each other. Information delivered over a channel should be authenticated as to origin, date of origin, data content, time sent, etc. Data origin authentication implicitly provides data integrity.

- *Non-repudiation* prevents an entity from denying previous actions. When disputes arise due to an entity denying that certain

actions were taken, a means to resolve the situation is necessary. For example, one entity may authorize the purchase of property by another entity and later deny such authorization was granted.

# 2.2.2 Symmetric Cryptography Primitives

Cryptosystems are divided between *secret-key* or *symmetric*, *public-key* or *asymmetric* and *unkeyed* systems. Asymmetric cryptography is built around mathematical hard problems [61] such as factorization, discrete logarithms or elliptic curves. Some approaches to public-key cryptography for RFID based on re-encryption and Elliptic Curve Cryptography are detailed in [49, 11]. Nevertheless, current EPC Gen2 tag computation capabilities are unsuited to asymmetric cryptography deployment [27]. The unkeyed cryptography main example is the *Hash* functions. The cost of these hash functions in hardware implementation is considered expensive in the literature [27]. Due to the excessive consumption of hash functions regarding computational power and memory resources it is recommended to minimize its use in RFID implementations and consider alternative security tools [29].

Symmetric cryptography is based on the secret-key exchange between participants. There are two distinct types of symmetric encryption; *stream ciphers* and *block ciphers* and their functionality is described as follows [72]:

• A *block cipher* transforms blocks of plaintext into ciphertext under the action of a key. This is typically a relatively complicated transformation but, apart from the reused key, the encryption of one block is independent of another.

• A stream cipher generates a keystream by sampling a constantly evolving cipher state. The state is typically initialized under the action of a key and an initialization vector. The sampling operation and the operation used to update the state are usually computationally lightweight. The plaintext stream is then encrypted by combining it directly (typically using bitwise XOR) with the keystream to give the ciphertext stream.

The Data Encryption Standard (DES) algorithm has been the most important block cipher for decades. Due to its limited key size (56bit) this algorithm was extended with the Triple-DES and now it has been replaced by the Advanced Encryption Standard (AES) algorithm which uses 128, 192 and 256-bit keys. The AES algorithm was standardized by the NIST [4] in 2001. Other interesting block ciphers for resource constrained devices are the Tiny Encryption Algorithm (TEA) [99] and the Present Algorithm [13]. The latter is currently the most hardware efficient block cipher with 1,570 GE. TEA, DES and AES block ciphers can be implemented from around 2,000 GE [72].

Together with the block cipher, symmetric cryptography includes the stream cipher. The remainder of this section deepens into this category of ciphers and the keystream generators used by the stream ciphers, usually pseudo-random number generators.

# 2.2.3 Pseudo-Random Number Generators

The security of many cryptographic systems depends upon the generation of unpredictable data sequences [61], for example the keystream in the *one-time-pad* or the challenges used in challenge-response identification systems. In any case, the generated sequences must be of sufficient size and be random in the sense that any generated sequence must have the same probability of appearance, to avoid the possibility of a search strategy based on such probability from an adversary.

A random number generator (RNG) is a device or algorithm which outputs a sequence of statistically independent and unbiased binary digits. However RNG is an inefficient procedure in most practical environments [61]. A PRNG is a deterministic algorithm which given an initial state (or seed) of length k, outputs a binary sequence of length  $l \gg k$  which looks like a random sequence. It is usually a deterministic one-way algorithm that generates sequences which statistical properties are indistinguishable from truly random numbers, but its output is often predictable [16]. PRNGs are characterized by its period, lineal complexity and implementability, and must fulfill the three Golomb's postulates [87, 36]:

- 1. The number of 1's in every period must differ from the number of 0's by no more than one.

- 2. In every period, half the runs must have length one, one quarter must have length two, one eighth must have length three ... as long as the number of runs so indicated exceeds one. Moreover, for each of these lengths, there must be just as many runs of 1's and 0's.

- 3. Suppose we have two copies of the same sequence of period p which are off-set by some amount d. Then for each d,  $0 \le d \le p-1$  we can count the number of agreements between the two sequences,  $A_d$ , and the number of disagreements,  $D_d$ . Then, the auto-correlation coefficient for each d, defined by  $(A_d D_d)/p$ , must be a bi-valuated function.

Many cryptographic algorithms and protocols require the generation of random values such as keys (or keystreams) and nonces, hence, the generated random sequences need to be unpredictable in practice. As specified in the EPC Gen2 Standard the tags should include a PRNG, whose main function is the generation of RN16s to be used as onetime pad nonce for data encryption.

A PRNG functionality is typically based on some unknown secret to the adversary, for example the generator internal state. The PRNG computes the next output sequence as a one-way function of its internal state, adapting the internal state in a deterministic manner. Good PRNGs are designed in such a way that they satisfy the following properties [16]:

- The adversary cannot compute the internal state of the PRNG, even if many outputs of the PRNG have been observed.

- The adversary cannot compute the next output of the PRNG, even if many previous outputs of the PRNG have been observed.

- If the adversary can observe or even manipulate the input samples that are fed in the PRNG, but the internal state of the PRNG is not known, then the adversary cannot compute the next output and the next internal state of the PRNG.

- If the adversary has somehow learned the internal state of the PRNG, but the input samples that are fed in the PRNG cannot be observed, then the adversary cannot figure out the internal state of the PRNG after the re-keying operation.

PRNGs play an important role when trying to encrypt plaintext messages in an information constrained environment. PRNGs are generally fast and have a simply hardware circuitry, solving the absence of buffering and being suitable for highly probable error-transmission channels [61]. Next, two common PRNGs are introduced: the Lineal Congruential Generator (LCG) and the Linear Feedback Shift Register (LFSR).

#### Lineal Congruential Generator

Lineal Congruential Generators (LCG) presented by Lehmer in 1951 [54] are pseudo-random number generators defined by equation 2.2, in which  $X_i$  is the  $i_{th}$  number of the sequence, and  $X_{i-1}$  is the previous number of the sequence. Variables a, b and m are constants and  $X_0$  is the seed or key of the system.

$$X_i = (aX_{i-1} + b) \mod m$$

(2.2)

If a, b and m are properly chosen, then the generator will be a maximal period generator and the output of the sequence will have period of m [90]. Regardless of its good statistical properties and easy implementation in software, LCGs are easily predictable (even if parameters a, b and m are unknown) because only a few integers produced by the LCG are necessary to predict the remainder of the sequence [77]. Hence, LCGs are not suitable for cryptographic applications [73].

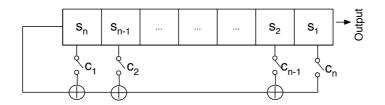

#### Linear Feedback Shift Registers

A linear feedback shift register (LFSR) (cf. Figure 2.6) is a digital circuit of n bits (or cells) that contains a shift register and a feedback function. The shift register is composed of a sequence of binary cells that share the same clock signal. Each time a bit is needed, the con-

Figure 2.6: Linear feedback shift register scheme

tent of the register is shifted one cell, obtaining the most significant bit of the register in the previous state, given by the expression:

$$s_{n+1} = c_1 s_n + \dots + c_n s_1 \tag{2.3}$$

The feedback function computes a new bit using the current state of the register, obtaining the less significant bit to be filled in the new state of the register. The feedback function of a LFSR can be represented as a polynomial function of degree n:

$$C(x) = 1 + c_1 x^1 + c_2 x^2 + \dots + c_n x^n$$

(2.4)

The feedback polynomial function is defined by the value of the coefficients  $c_i \in \{0, 1\}$ . If  $c_i = 1$ , the content of the cell n - i (named *tap*) is used to compute the new most significant bit of the register. Tap's content is processed with an exclusive OR logical operation (XOR).

The LFSR can then be determined by this polynomial function. In turn, the sequences of the LFSR can be determined by the polynomial function of the LFSR and the initial state of the register cells (often referred as *seed*). Equation 2.5 shows the mathematical expression of the LFSR where n is the number of cells of the LFSR, i is the position in the register and k is the number of shifts. It is important to notice that an initial state with zeros in all the cells leads to an absorbing state, generating zeros for the following shifts of the LFSR.

$$s_{n+k} = \sum_{i=1}^{n} c_i s_{n+k-i} \tag{2.5}$$

The period (quantity of different possible states) of a LFSR with n cells is up to  $2^n - 1$  when taps configuration follows a primitive polynomial function, generating sequences with optimum statistical properties. A primitive polynomial is a polynomial that generates all elements of an extension field from a base field. Primitive polynomials are also irreducible polynomials. For example, the number of primitive polynomials of degree n over the finite field GF(2) (i.e., with coefficients either 0 or 1) is defined by the Equation 2.6, where  $\phi(n)$  is the *totient* function [12].

$$a_2(n) = \frac{\phi(2^n - 1)}{n} \tag{2.6}$$

LFSRs are the most common type of shift registers used in cryptography. They lead to efficient and simple hardware implementations. They have, however, important drawbacks that must be handled. First, the sequences of a LFSR are predictable [41, 19]. For example, let  $s_{k+1}, s_{k+2}, \dots, s_{k+2n}$  be a sequence of 2n consecutive bits generated from a LFSR. Let  $c_n, c_{n-1}, \dots, c_1$  be the feedback function of the LFSR. Then, the feedback function can be easily computed by solving the following equation system:

$$\begin{bmatrix} s_{k+1} & s_{k+2} & \cdots & s_{k+n} \\ s_{k+2} & s_{k+3} & \cdots & s_{k+n+1} \\ \vdots & \vdots & \ddots & \vdots \\ s_{k+n} & s_{k+n+1} & \cdots & s_{k+2n-1} \end{bmatrix} \begin{bmatrix} c_n \\ c_{n-1} \\ \vdots \\ c_1 \end{bmatrix} = \begin{bmatrix} s_{k+n+1} \\ s_{k+n+2} \\ \vdots \\ s_{k+2n} \end{bmatrix}$$

(2.7)

By solving Equation 2.7 we obtain the feedback polynomial coefficients. Therefore, a *n*-bit (cells) LFSR with period  $2^n - 1$  can be determined with only 2n values. The *Berlekamp-Massey* [57] algorithm can also be used to solve the feedback coefficients of a LFSR with only 2n values. Since any periodic sequence can be generated with a LFSR, the *linear complexity* of a sequence is defined as the shortest number of LFSR cells that can generate the sequence. In other words, if we define L(s) as the linear complexity of an infinite binary sequence s, then [61]:

- if s is the zero sequence  $s = 0, 0, 0, \dots$  then L(s) = 0

- if no LFSR generates s, then  $L(s) = \infty$

- otherwise, L(s) is the length of the shortest LFSR that generates s.

This linearity problem must be handled before using LFSRs to build PRNGs.

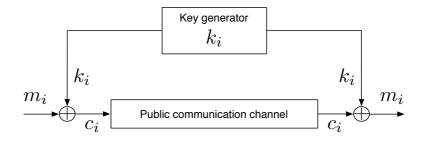

# 2.2.4 Stream Ciphers

Stream ciphers (cf. Figure 2.7) are an important class of encryption algorithms. They encrypt individual values (usually bits) of a plaintext message one at a time, using an encryption transformation

Figure 2.7: Working principle of stream cipher

which varies with time [61]. The stream cipher algorithms are the most simple symmetric cryptographic primitives. The encryption is applied to a single bit for each cycle (usually applying a XOR operation) with a key stream that depends on the current internal state. Pseudo-random number generators are the main components of the stream ciphers, since long keys with good statistical properties are necessary for the suitable performance of stream ciphers.

The classic stream cipher example is the Vernam Cipher, defined by Equation 2.8. Where  $m_1, m_2, m_3, \ldots$  are the plaintext digits,  $k_1, k_2, k_3, \ldots$  are the keystream digits and  $c_1, c_2, c_3, \ldots$  are the ciphertext digits. The symbol  $\oplus$  denotes the XOR operation (bitwise addition modulo 2), and the decryption is defined by  $m_i = c_i \oplus k_i$ . If the keystream digits are generated independently and randomly, the Vernam Cipher is called the *one-time-pad*, and is unconditionally secure against a ciphertext-only attack. Shannon proved that a necessary condition for a symmetric-key encryption scheme to be unconditionally secure is that the uncertainty of the secret key must be at least as large as the uncertainty of the plaintext [92]. The one-time-pad is unconditionally secure regardless of the statistical distribution of the plaintext.

$$c_i = m_i \oplus k_i \tag{2.8}$$

An obvious drawback of the one-time-pad is that the key should be as long as the plaintext, which represents a problem for the key management or distribution. This motivates the design of stream ciphers where the keystream is pseudo-randomly generated from a smaller secret key. Such stream ciphers do not offer unconditional security (since the key is smaller than the plaintext), but they are designed with the aim to be computationally secure [61].

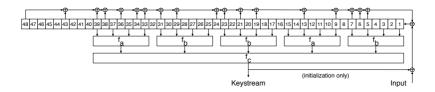

## Stream ciphers based on LFSRs

LFSRs are used as keystream generators due to their suitable properties for hardware implementation, producing sequences with large periods and good statistical properties. Since well-designed systems should be secure against known-plaintext attacks, a LFSR should never be used by itself as a keystream generator because of its predictability. Nevertheless, LFSRs are desirable because of their very low implementation costs, large periods and good statistical properties. Two general methodologies for avoiding the linearity properties of LFSRs are used:

- Using a nonlinear filtering function on the contents of one (or more) LFSRs

- Using the output of one (or more) LFSRs to control the clock of one (or more) other LFSRs.

Filters use a nonlinear feedback function as an input to the register. The filter should not be too simple to be weak but neither too complex, otherwise it would become the bottleneck of the generator. However recent attacks to the MIFARE PRNG [30] have demonstrated the vulnerability of this kind of generators when the nonlinear function is not taken carefully. Another example of nonlinear filter generators is the *Knapsack generator* developed by Merkle and Hellman [62].

Another approach to break the linearity of a LFSR is to use a nonlinear combination of multiple LFSRs to generate a unique output. Generally, the output of one LFSR is used to select or combine the output of one or more LFSRs, in the same or different clock times. Known examples of this approach are the Geffe [33], A5 [90] or the Shrinking generator [90]. The output generated from this constructions is statistically weak, being vulnerable to correlation or sidechannel attacks [47]. Also the irregular output data rate from some of these constructions (e.g. the shrinking generator) is not suitable for PRNG used in security environments.

Another strategy for the security improvement of LFSR based stream ciphers is to keep the feedback connection polynomial secret. For known connections, the secret key generally consists of the initial contents of the component LFSRs. For secret connections, the secret key for the keystream generator generally consists of both the initial contents (or initialization vector) and the connections polynomial.

# 2.3 Stream Ciphers for RFID Constrained Devices

In the remainder of this section some stream ciphers and pseudorandom number generators specifically designed for constrained devices (e.g. EPC Gen2 devices) are introduced. Since the ratification of the EPC Gen2 specification [25] and the ISO standards ISO/IEC 18000-6C [6], in which the usage of on-tag PRNGs on low-cost RFID devices is presented as mandatory, the number of stream ciphers for security solutions has increased in the industry and academic research. Cryptographic suitable PRNGs designs must satisfy, in addition to a low hardware complexity, some other relevant properties. A crucial property that stream ciphers designed for security purposes must address is unpredictability. Indeed, an external adversary who eavesdrops the communication cannot compute the PRNG internal state, even if many outputs of the generator have been observed. The adversary cannot either compute the next sequence, even if many other previous sequences have been observed. If the adversary can observe, or even manipulate, the input samples that are fed by a PRNG, but its internal state is not known, the adversary must not be able to compute the next sequence or the next internal state of the PRNG. Finally, if the adversary has somehow learned the internal state of the PRNG, but the input samples that are fed in cannot be observed, then the adversary should not figure out the internal state of the PRNG after the re-keying operation.