# Seguridad en redes y aplicaciones distribuidas Análisis de la detección de emulación basada en tiempos

José Miguel Fernández Sánchez Master en seguridad de las TIC

Seguridad en redes y aplicaciones distribuidas Análisis de la detección de emulación basada en tiempos

> Profesor colaborador: Ángel Elbaz Sanz Profesor responsable: Guille Navarro Arribas

#### **RESUMEN**

El objetivo de este trabajo de fin de master es analizar las técnicas de detección de emulación basada en el análisis de tiempos de ejecución que podrían ser usadas por el *malware*, buscar una solución general para evitar las detecciones mencionadas, e implementar una prueba de concepto que permita evaluar la viabilidad de la solución propuesta.

Se han desarrollado diversos ejemplos de detección, concluyendo que una solución sería que el emulador incorporase a la emulación aspectos relativos a la implementación de la arquitectura. Se ha desarrollado una prueba de concepto basada en la solución propuesta, y se ha comprobado que dicha prueba de concepto es capaz de evitar la detección de todos los ejemplos presentados.

#### **ABSTRACT**

The goal of this Master's Thesis is to analyze time based emulation detection techniques who could be used by malware, propose a general solution to avoid those detection techniques and implement a proof of concept to assess the viability of the proposed solution.

Several detection examples have been developed, inferring that a plausible solution could be to incorporate arquitectural implementation details to the emulation. A proof of concept has been developed based on the proposed solution, and it has been proven that it is able to avoid the detection of the provided detection examples.

| 1.Introducción                                    | 5  |

|---------------------------------------------------|----|

| 2.Trabajos previos                                | 5  |

| 3. Malware                                        | 6  |

| 3.1. Definición                                   | 6  |

| 3.2. Clasificación                                | 6  |

| 4. Emulación                                      | 7  |

| 4.1. Definición                                   | 7  |

| 4.2. Clasificación de la emulación                | 7  |

| 4.3. La emulación en la detección de malware      | 8  |

| 5. Elección del emulador                          | 8  |

| 5.1. Requisitos                                   | 8  |

| 5.2. Emuladores contemplados                      | 9  |

| 5.3. Emulador seleccionado                        | 10 |

| 6. Detección de emulación                         | 10 |

| 6.1. Introducción                                 | 10 |

| 6.2. Descripción de la Microarquitectura x64      | 11 |

| 6.3. Consideraciones iniciales                    | 15 |

| 6.4. Ejemplo 1: Rendimiento de las instrucciones  | 17 |

| 6.5. Ejemplo 2: Optimizaciones en allocate/rename | 18 |

| 6.6. Ejemplo 3: Super escalar                     | 19 |

| 6.7. Ejemplo 4: Comportamiento de la Caché        | 20 |

| 6.8. Ejemplo 5: Comportamiento de la Caché (2)    | 21 |

| 6.9. Ejemplo 6: Reenvío de datos                  | 22 |

| 6.10. Ejemplo 7: Macro fusión                     | 23 |

| 6.11. Ejemplo 8: Delaminación                     | 25 |

| 6.12. Ejemplo 9: Determinismo                     | 25 |

| 6.13. Ejemplo 10: Micro Fusión                    | 26 |

| 6.14. Otras pruebas                               | 27 |

| 7. Evitando la Detección                          | 30 |

| 7.1. Introducción                                 | 30 |

| 7.2. Organización                                 | 31 |

| 7.3. Ajuste del tiempo de ejecución               | 31 |

| 7.4. La instrucción RDTSC                         | 32 |

| 7.5. Latencia y rendimiento de las instrucciones  | 32 |

| 7.6. Emulación de la caché                        | 33 |

| 7.7. Emulación de reenvío de datos                | 34 |

| 7.8. Emulación de macro fusión                       | 34 |

|------------------------------------------------------|----|

| 7.9. Emulación de la Micro fusión, y la delaminación | 35 |

| 7.10. Emulación de la predicción de saltos           | 36 |

| 8. Conclusiones                                      | 36 |

| 9. Posibles direcciones futuras                      | 38 |

| 10. Referencias                                      | 38 |

# 1.Introducción

La emulación es uno de los mecanismos usados comúnmente en la detección y el análisis de malware [Po07], [Gy09], [Eg09], [Kr14], [St05]. El rendimiento del emulador, así como la exactitud de la emulación son aspectos claves a la hora de definir la capacidad real del emulador para llevar a cabo las tareas de detección y análisis. A lo largo de los años el *malware* ha ido buscando soluciones cada vez más elaboradas e implementando técnicas evasivas que dificultan su detección. Evitar la emulación, o modificar su comportamiento en entornos emulados ha sido una de las técnicas utilizadas. La capacidad del *malware* para implementar dichas técnicas se basa en las diferencias observables entre el sistema emulado y el sistema real.

Este trabajo explora los límites de la emulación y las posibles técnicas de detección basadas en los tiempos de ejecución de diversos trozos de código binario. El trabajo se limita a estudiar la emulación del procesador, dejado de lado otros elementos, como puede ser la emulación del sistema operativo. De la misma forma, el trabajo se centra en la arquitectura x64, aunque muchos de los resultados obtenidos se pueden extrapolar a otras arquitecturas.

Se presentan como resultado de la investigación diversos ejemplos de detección. Del estudio de los ejemplos de detección expuestos, se concluye que el problema fundamental en la emulación es que no tiene en cuenta los detalles de la implementación de la arquitectura, detalles que en muchos casos tienen efectos que se pueden observar en el procesador real, y por lo tanto deberían poder observarse en el entorno emulado.

Se presenta, así mismo, una prueba de concepto consistente en una emulación rudimentaria de la microarquitectura del procesador. Esta prueba de concepto permite que un emulador seleccionado pueda ejecutar los ejemplos expuestos sin que la emulación sea detectada. El trabajo concluye que el uso de un emulador implementado de forma que emulase la microarquitectura del procesador proporcionaría un entorno más difícil de diferenciar del entorno real, lo que tendría un impacto positivo en la lucha contra el *malware*. También se concluye que dicha implementación no es trivial, siendo la falta de documentación respecto de la microarquitectura y su rendimiento dos aspectos críticos y a tener en cuenta.

# 2. Trabajos previos

Existen gran cantidad de trabajos sobre el uso de la emulación y su papel en el análisis y detección de *malware*. Algunos ejemplos pueden ser [Po07], [Gy09] o [Eg09]. Los trabajos que analizan los límites actuales de su uso son más escasos y carecen de la profundidad de los primeros. Es notable destacar que la inmensa mayoría de los trabajos, si no todos ellos, se centran en la arquitectura x86.

En lo tocante a la detección del entorno, la virtualización ha atraído cierta atención, con trabajos bien conocidos, como [Ru05], que generó un gran debate, y con trabajos interesantes como [5], [To10], o recientemente [As17]. Ideas como la expuesta en [Ru05], basada en discrepancias en la dirección de memoria en la que se alojan estructuras globales a nivel de sistema operativo¹, no se pueden aplican al caso de la emulación. Sin embargo, algunas ideas expuestas en [Fr08] y analizadas en detalle en [To10] son totalmente aplicables a la detección de emulación. En el trabajo mencionado se expone un análisis basado en el tiempo de ejecución, y un estudio sobre los efectos de la virtualización sobre la caché.

Los trabajos en la detección de sistemas de emulación escasean y tratan el tema en menor detalle. Por ejemplo, [Na14] expone varios métodos que podrían ser usados por un malware para evitar su detección mediante la emulación. En todos los casos, la idea subyacente es que la emulación no es lo suficientemente precisa o lo suficientemente rápida como para emular

<sup>&</sup>lt;sup>1</sup> Un sistema operativo virtualizado duplica estructuras como tablas de descriptores de interrupciones, tablas de descriptores globales, etc. Normalmente, un sistema operativo almacena estas estructuras en direcciones de memoria específicas. En el sistema virtualizado, se puede observar que dichas estructuras se encuentran en direcciones de memoria diferentes.

adecuadamente un trozo de código. Los ejemplos propuestos en este trabajo se centran exclusivamente, por tanto, en problemas asociados a la calidad de la implementación. Un trabajo más interesante es [Ra07], que hace referencia tanto a la detección de virtualización como de emulación. En concreto, en el caso de la emulación, el trabajo propone varios mecanismos de detección. Entre ellos, propone la detección de emulación basada en el análisis de tiempos relativos tanto en la ejecución de instrucciones² como en el comportamiento de la caché. El trabajo [Bl16] también expone varios mecanismos para la detección de emulación, entre los que cuenta la detección de tiempos. En este caso, propone la detección usando mediciones de tiempos absolutas basadas en invocaciones a servicios del sistema³. [Eg09] y [Ga04] también mencionan la detección de emulación basada en discrepancias en los tiempos, tanto relativos como absolutos.

Como se puede apreciar, los trabajos consultados tratan la detección de emulación basada en la diferencia de tiempos, pero lo hacen de forma superficial. Solamente se analizan tres casos: Los análisis relativos y absoluto de tiempos, y el efecto de la caché en los tiempos de ejecución en un entorno emulado con respecto al entorno real.

## 3. Malware

### 3.1. Definición

El término *malware* surge de la combinación de dos palabras: *malicious* y *software*. Este término se usa para hacer referencia a cualquier *software* no deseado, y es definido en [Mc00] como cualquier código añadido, modificado o eliminado de un sistema informático con el objetivo de causar daño o modificar el comportamiento previsto del sistema.

El *malware* se caracteriza por su capacidad para auto replicarse y para propagarse, para auto ejecutarse, para persistir en un sistema, y para evitar su análisis. Entre las propiedades del *malware* que evitan el análisis se encuentran la anti máquina virtual, la anti depuración, la anti emulación, el cifrado, y el empaquetado [Le13].

## 3.2. Clasificación

El *malware* se suele clasificar normalmente basándose en su comportamiento. Por ejemplo, virus para el *malware* que se replica modificando los programas informáticos instalados en el sistema informático, gusano para el *malware* que se propaga de computadora a computadora usando las conexiones de red, o puerta trasera para el malware que modifica un sistema informático habilitando un mecanismo para acceder al sistema evitando sus sistemas de seguridad. En algunos casos, virus se ha utilizado en castellano como un término genérico, siendo prácticamente un sinónimo de *malware*.

La clasificación del *malware* basándose en su comportamiento principal resulta insuficiente debido a dos razones.

Primero, no es lo suficientemente explicativa, de forma que una segunda clasificación basada en aspectos técnicos del *malware* es usada, mezclándose con la clasificación basada en comportamiento, y dando como resultado una clasificación poco intuitiva. Así, por ejemplo, un

<sup>&</sup>lt;sup>2</sup> Comparando el tiempo de ejecución de una instrucción relativamente lenta, con una instrucción relativamente rápida

<sup>&</sup>lt;sup>3</sup> Por ejemplo, invocar a la función Sleep, usando como argumento 1000ms

virus puede sub clasificarse en residente o no residente, pero también en EPO<sup>4</sup>, polimórfico<sup>5</sup>, etc. El problema fundamental es que esta clasificación, basada en detalles técnicos, no es mutuamente excluyente, de forma que un virus puede utilizar varias de las técnicas mencionadas. Es más, algunas de las técnicas pueden ser usadas por otro *malware* que no pertenece a la categoría virus.

La segunda de las razones está relacionada con la creciente complejidad del *malware*, que hace que tengan varios comportamientos de la clasificación al mismo tiempo, lo que a su vez ha llevado a que los analistas de *malware* clasifiquen el mismo *malware* con tipos diferentes. Una clasificación sin ambigüedades ha sido propuesta en [Le13], basada en observaciones del comportamiento del *malware* a bajo nivel.

# 4. Emulación

## 4.1. Definición

La emulación consiste en proporcionar un entorno simulado a una aplicación o código binario, de forma que dicho entorno simulado se comporta como el entorno real para el que la aplicación fue creado.

La creación de dicho entorno simulado conlleva el modelar distintos componentes *hardware* como el procesador y algunos chips del sistema, como controladores de interrupciones o de bus, DMA, etc.), dispositivos de entrada/salida, un posiblemente un sistema operativo.

### 4.2. Clasificación de la emulación

Se han estudiado diversos aspectos importantes en la emulación, que pueden dar lugar a diversas clasificaciones posibles [Ti00]. Por ejemplo, desde el punto de vista de la exactitud de la emulación, se pueden definir varios niveles. Otra posible clasificación podría basarse en el grado de emulación. Esto es, en cuanto del sistema es basado en *software* y cuanto en *hardware*.

En algunos trabajos, la virtualización se contempla como un caso específico de emulación. En lo que se refiere al presente trabajo, se opta por una visión más restringida del concepto de emulación, separado del de virtualización, en la línea de trabajos como [Wa15]. En este caso, la característica fundamental que permite diferenciar entre emulación y virtualización es que la primera no comparte necesariamente ninguna característica física entre el sistema emulado y el sistema en el que dicho emulador se ejecuta. Existe otra característica importante que diferencia ambos sistemas. En el caso de los sistemas emulados, el grado de control sobre el código emulado es mucho mayor, y este mayor control no es una diferencia cuantitativa, sino cualitativa, puesto que permite un análisis detallado del código emulado sin que la emulación en sí misma se vea afectada, lo cual no es posible en el caso de los sistemas virtualizados [Kr14].

<sup>&</sup>lt;sup>4</sup> Entry Point Obfuscation. Este tipo de virus intenta, al llevar a cabo la infección de un fichero, que el punto de entrada del ejecutable no se modifique sustancialmente.

<sup>&</sup>lt;sup>5</sup> Al infectar otras aplicaciones, los virus polimórficos generan copias de sí mismos con variaciones respecto al virus original. Estas variaciones no modifican el comportamiento del virus, y se llevan a cabo normalmente cifrando partes del virus con una clave aleatoria. Se pueden encontrar casos más elaborados que utilizan algoritmos de selección de instrucciones o asignación de registros con el objetivo de generar un conjunto de instrucciones diferente en cada infección.

### 4.3. La emulación en la detección de malware

Como se describe en [Sz01], la emulación fue una de las piezas clave en la lucha contra el *malware* cuando los virus polimórficos comenzaron a hacerse más comunes. Desde entonces, los sistemas de emulación han sido usados de forma habitual para el análisis y la clasificación de *malware* [Gy09], [Kr14].

Como se menciona en [Kr14], aunque la emulación es un mecanismo eficaz desde el punto de vista teórico, la aplicación práctica de esta idea encuentra diversas dificultades. Una de ellas es la necesidad de emular un sistema operativo relativamente complejo, y con muchos detalles no documentados. Lo mismo se puede decir del procesador, donde la documentación de la arquitectura del juego de instrucciones no es suficiente para llevar a cabo una emulación fidedigna, y donde los detalles de la microarquitectura no están siempre completamente documentados.

Otro de los problemas clave asociados a la emulación es el tiempo de ejecución del código emulado. Cada instrucción del programa emulado se puede traducir en decenas o cientos de instrucciones ejecutadas para su emulación. Se han estudiado diversos mecanismos y técnicas para mejorar el rendimiento de la emulación, como por ejemplo [St05]. Nótese que, a pesar del título de trabajo, el resultado final sigue teniendo cabida en la definición de emulación usada.

# 5. Elección del emulador

## 5.1. Requisitos

Dado que el estudio se centra en las detecciones de emulación basadas en tiempos, el emulador elegido debe cumplir como mínimo los siguientes requisitos:

- Debe tratarse de un emulador basado solamente en software. Esto es, quedan excluidos los sistemas de emulación que hacen uso de virtualización<sup>6</sup>, parcial o totalmente. Este requisito es necesario debido al grado de control y cantidad de información que un sistema de emulación orientado al análisis de *malware* necesita<sup>7</sup>.

- Debe ser un emulador con código abierto, con una licencia compatible con este trabajo de fin de master, y debe ser gratuito.

- Debe emular correctamente el juego de instrucciones completo de la arquitectura x86, tanto de 32 bits como de 64 bits<sup>8</sup>.

- Debe proporcionar un rendimiento aceptable. Es difícil enunciar este requisito de forma objetiva. Un emulador utilizado en el análisis de *malware* debe proporcionar un alto rendimiento debido a algunos sus casos de uso típicos. Por ejemplo, una pasarela de correo puede recibir miles de correos por hora. Un producto de seguridad puede analizar todos los ficheros adjuntos a

<sup>&</sup>lt;sup>6</sup> Ya se había mencionado que la definición de emulación usada en este documento no incluye la virtualización. Se menciona de nuevo la virtualización en este apartado dado que podrían existir sistemas híbridos haciendo uso de la virtualización.

<sup>&</sup>lt;sup>7</sup> En este sentido, se pueden consultar los criterios formales para la virtualización, por Popek y Goldsberg [Po74], donde se puede apreciar que uno de ellos es que una cantidad notable de las instrucciones máquina deben ser ejecutadas sin intervención del sistema de virtualización. Como es obvio, este criterio limita notablemente la posibilidad de extraer información o de analizar el código emulado. Aunque el documento mencionado es antiguo, su contenido sigue estando, esencialmente, vigente.

<sup>&</sup>lt;sup>8</sup> Se excluye la emulación de algunos detalles de la arquitectura, como contadores de rendimiento, registros o instrucciones presentes en versiones específicas del procesador, etc.

los correos. Los ficheros ejecutables son analizados, y durante dicho análisis son emulados para obtener información sobre su comportamiento, como parte del proceso de desempaquetado si se detecta que el ejecutable está empaquetado, para aplicar firmas que dependan directamente de la emulación, etc. La emulación debe ser lo suficientemente rápida como para que la pasarela no se convierta en un cuello de botella. Todo lo dicho para el ejemplo anterior también se aplica a otros escenarios donde le rendimiento es aún más crítico. Por ejemplo, una suite de seguridad instalada en un equipo de escritorio puede contar con un componente residente que analice los ficheros a los que se accede. Al ejecutar una aplicación, el residente analiza el fichero ejecutable antes de permitir su ejecución. Un emulador demasiado lento tendría en este caso un efecto negativo evidente al demorar el comienzo de la ejecución de todas las aplicaciones.

Informalmente, este requisito se podría enunciar como la necesidad de que el rendimiento del emulador sea los suficientemente bueno como para que pueda ser considerado para su uso en un producto de seguridad. Podemos asumir que, si un emulador implementa técnicas orientadas a la mejora del rendimiento, dicho emulador será aceptable. La traducción dinámica de código<sup>9</sup> es quizás la más conocida de estas técnicas, pero no la única. La evaluación deferida de flags<sup>10</sup>, las optimizaciones basadas en caché de trazas<sup>11</sup>, u optimizaciones relacionadas con la traslación de páginas son otras técnicas que pueden mejorar notablemente el rendimiento de un emulador.

Además de los requisitos expuestos anteriormente, existen otras cualidades deseables:

- Tratarse de un emulador cuyo uso sea lo más simple posible. En este caso simple significa simplicidad y conveniencia en cuanto a interfaces, buena documentación y acceso a ejemplos útiles.

- Poder emular diversas plataformas. Aunque inicialmente el trabajo se centra en la arquitectura x86, no se descarta el llevar pruebas básicas en otras plataformas.

- Poder ejecutar trozos arbitrarios de código. Es decir, que no sea necesario generar un fichero ejecutable de un formato específico para poder llevar a cabo una prueba en el emulador. Esta flexibilidad agilizaría el trabajo y permitiría llevar a cabo más pruebas.

## 5.2. Emuladores contemplados

El primero de los emuladores que se han contemplado como base para el trabajo es Qemu<sup>12</sup>. Este emulador proporciona un gran número de funcionalidades, entre las que se encuentra la virtualización, la emulación a nivel de sistema (incluyendo la emulación de periféricos), y además proporciona un buen rendimiento. Como se indica en su documentación, el emulador implementa la traducción dinámica de código con el fin de optimizar su rendimiento. Además, es capaz de emular diferentes arquitecturas (x86, ARM, MIPS, etc.)

9

<sup>&</sup>lt;sup>9</sup> La traducción dinámica de código es una técnica basada en la compilación en tiempo de ejecución, de forma que el código emulado es convertido en código que puede ser ejecutado de forma nativa. Esta técnica, también conocida como *JIT* (*Just-In-Time*) es clave en la implementación de las máquinas virtuales de muchos lenguajes interpretados.

<sup>&</sup>lt;sup>10</sup> Lazy Flags Evaluation en inglés. En un procesador, cada operación llevada a cabo por las unidades aritmético-lógicas actualiza el registro de *flags* de acuerdo con los resultados de las operaciones. Un emulador puede ignorar dicha actualización si ello no afecta la corrección de la emulación.

<sup>&</sup>lt;sup>11</sup> Una caché de trazas almacena información de las instrucciones ejecutadas, de forma que si la misma instrucción se vuelve a ejecutar en un futuro cercano no es necesario volver a descodificar la instrucción desde cero. Este tipo de optimizaciones se pueden ver tanto en emuladores como en la implementación de microarquitecturas. En el caso de los procesadores Intel x86, esta caché se suele llamar *DSB* (*Decoded Stream Buffer*), *Decoded ICache*, o *Decoded μop Cache*.

<sup>12</sup> https://www.gemu.org

Otro de los emuladores contemplados es Bochs<sup>13</sup>. Al igual que Qemu, Bochs emula no solo el procesador, sino también un conjunto de periféricos y una BIOS ad hoc, proporcionando una emulación a nivel de sistema. Las principales diferencias entre Bochs y Qemu son:

- Bochs es más lento que Qemu, implementando algunas optimizaciones como la evaluación deferida de los *flags*, pero sin llegar al rendimiento ofrecido por Qemu.

- Bochs se centra exclusivamente en la arquitectura x86

Unicorn es un proyecto basado en Qemu, pero que se centra en la emulación del procesador, dejando de lado el intentar emular un sistema completo. Debido a centrarse exclusivamente en la emulación del procesador, su interfaz de usuario es sencilla, comparada con Qemu, y además permite la ejecución arbitraria de trozos de código binario.

Proyectos como VirtualBox<sup>14</sup> y Xen<sup>15</sup> se basan exclusivamente en la virtualización, por lo que no cumplen con los requisitos exigidos por este trabajo.

JPC¹6 es un emulador de x86 implementado en Java, y que pretende ofrecer una emulación a nivel de sistema, similar A Bochs, por ejemplo. Intenta explotar las optimizaciones existentes en la máquina virtual de Java para llevar a cabo una emulación con un rendimiento razonable. Otro proyecto similar es Dioscuri¹7, basado en JPC. Los dos problemas principales en estos dos proyectos son que no parece que exista un desarrollo activo (La última versión de JPC tiene cuatro años), y que no parece que puedan llevar a cabo una emulación muy fiable (La documentación indica que pueden emular Windows 95, pero no emula otros Windows más modernos correctamente)

#### 5.3. Emulador seleccionado

De todos los emuladores analizados, se seleccionaron Qemu y Unicorn, por ser los que mejor se adaptaban a los requisitos del proyecto. Tras revisar las interfaces disponibles, y llevar a cabo una pequeña prueba de concepto, se ha decidido elegir Unicorn, debido a que era el que ofrecía una interfaz más versátil y que se adaptaba mejor a las necesidades del trabajo. La posibilidad de poder ejecutar trozos arbitrarios de código de forma sencilla y pudiendo ignorar la inmensa mayoría de la configuración previa necesaria en otros sistemas es clave a la hora de tomar la decisión, dado que dicha capacidad ofrece una gran agilidad. Las posibilidades en lo tocante a instrumentación disponibles en Unicorn es otro de los aspectos decisivos, puesto que ofrecen el tipo de interfaz necesario para el análisis detallado llevado a cabo durante el análisis de *malware*, así como para el desarrollo de este trabajo.

# 6. Detección de emulación

#### 6.1. Introducción

Existen diversas opciones a la hora de detectar que el sistema bajo el que se ejecuta un código es un sistema emulado. La más obvia es detectar diferencias en el comportamiento debido a la implementación defectuosa o incompleta del juego de instrucciones de la arquitectura. En el caso de la emulación de un sistema completo, la misma idea se puede aplicar a los periféricos o al

<sup>13</sup> http://bochs.sourceforge.net

<sup>14</sup> https://www.virtualbox.org

<sup>15</sup> https://www.xenproject.org

<sup>16</sup> https://github.com/ianopolous/JPC

<sup>&</sup>lt;sup>17</sup> http://dioscuri.sourceforge.net/index.html

conjunto de servicios proporcionados por el sistema operativo. Eligiendo la opción más generalista y evitando hacer asunciones acerca del sistema operativo, una correcta emulación del juego de instrucciones no es suficiente para garantizar que la emulación no puede ser detectada. Trabajos anteriores han mostrado que el análisis de los tiempos de ejecución puede ser usado para llevar a cabo dicha detección [Ra07], [BI16], [Eg09], [Ga04].

Como se ha comentado, el presente trabajo pretende avanzar en esta dirección, mostrando que el problema fundamental es que la emulación debe tener en cuenta la microarquitectura subyacente, dado que ésta no queda oculta tras la arquitectura del juego de instrucciones. Ejemplos como [Li18] y [Ko18] evidencian que los ataques de canal lateral¹³ son factibles en los procesadores modernos, [Ya16] muestra cómo, desde 2014 y hasta la fecha de publicación del trabajo, el estudio de este tipo de ataques había ganado tracción y se había incrementado notablemente, y trabajos como [Wa07] muestran que existe una preocupación por su peligrosidad e interés en buscar soluciones que los impidan o dificulten.

Tomando como ejemplo la arquitectura x64, los apartados sucesivos abordan distintos aspectos de su microarquitectura y de cómo ésta afecta los tiempos de ejecución, efecto que no es visible cuando el mismo código es ejecutado en el emulador seleccionado. Dicha discrepancia puede usarse como prueba de emulación.

## 6.2. Descripción de la Microarquitectura x64

En este apartado se presenta una descripción general de la microarquitectura típica de los procesadores x64. La descripción se centra en los aspectos de la microarquitectura que pueden resultar útiles para entender mejor las explicaciones relativas a los ejemplos de detección de emulación expuestos en los siguientes apartados.

A no ser que se indique lo contrario, toda la información técnica mencionada relativa a los procesadores en éste, así como en los sucesivos apartados, se menciona en [ln16], [ln16-2] o [Fo18].

La arquitectura x64 es una arquitectura relativamente compleja, con instrucciones de tamaño variable, de entre 1 y 16 bytes. Estas instrucciones se traducen a un conjunto de instrucciones internas, más sencillas, llamadas *micro opcodes*. Son estos *micro opcodes* (  $\mu$ ops en lo sucesivo), lo que el procesador ejecuta. Su microarquitectura<sup>19</sup> es *super escalar*<sup>20</sup>, fuera de orden<sup>21</sup>, y *super pipelined*<sup>22</sup>.

Debido a la complejidad de su juego de instrucciones, los procesadores cuentan con un *front-end* relativamente complejo, encargado de la descodificación de las instrucciones, de su traducción en  $\mu$ ops, y de su almacenamiento en una cola de  $\mu$ ops pendientes de ser ejecutados. Dicha cola se denominada  $IDQ^{23}$ . Este proceso se lleva a cabo en el orden en el que las instrucciones aparecen en el programa.

<sup>&</sup>lt;sup>18</sup> Ataques basados en la propia implementación de un sistema

<sup>&</sup>lt;sup>19</sup> Obviamente, no es correcto hablar de una microarquitectura x64. Existen muchos procesadores x64 con implementaciones diferentes. Aquí se hace referencia a características que son comunes a todas las implementaciones. Cuando las características mencionadas sean aplicables solo a una microarquitectura concreta, se indicará usando su nombre.

<sup>&</sup>lt;sup>20</sup> Puede ejecutar varias instrucciones en paralelo

<sup>&</sup>lt;sup>21</sup> Puede ejecutar las instrucciones en un orden diferente al que aparecen en el código

<sup>&</sup>lt;sup>22</sup> Divide la ejecución de una instrucción en un número relativamente alto de fases, permitiendo que las primeras fases de la ejecución las instrucciones se ejecuten en paralelo con las fases finales de las instrucciones precedentes. Por ejemplo, la microarquitectura *Haswell*, introducida en 2013, puede llegar a estar ejecutando cerca de 200 instrucciones en paralelo.

<sup>&</sup>lt;sup>23</sup> Instruction Decode Queue

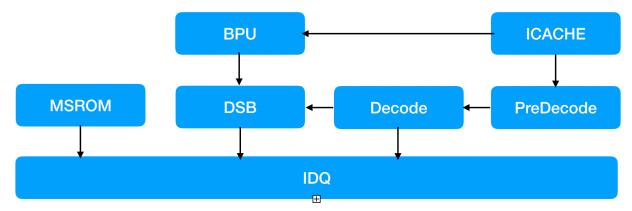

Fig 1: Visión esquemática del front-end

En la figura 1 se pueden ver los diferentes componentes que forman parte del *front-end*. El bloque *ICache* hace referencia a la caché de instrucciones<sup>24</sup>. El bloque denominado *PreDecode* se encarga de leer bloques de 16 bytes de la caché, de calcular el tamaño de cada instrucción en el bloque, y de proporcionar al elemento *Decode* las instrucciones encontradas<sup>25</sup>. El bloque *Decode* se encarga de descodificar las instrucciones, traduciéndolas en los μορs adecuados, y de enviarlos tanto a la cola *IDQ* como al *DSB*.

Los procesadores modernos tienen cuatro descodificadores. Tres de ellos son solo capaces de descodificar instrucciones sencillas que se convierten en un único  $\mu op$ , mientras que el cuarto descodificador puede descodificar instrucciones complejas, que se convierten en hasta cuatro  $\mu$ ops. El ancho de banda total es de hasta cinco  $\mu$ ops por ciclo. En el caso de encontrarse instrucciones muy complejas, que se traducen en más de cuatro  $\mu$ ops, es el componente  $MSROM^{26}$  el se encarga de su descodificación, generando cuatro  $\mu$ ops por ciclo hasta terminar de descodificar la instrucción.

El bloque DSB es una caché de  $\mu$ ops, y tiene un ancho de banda de seis  $\mu$ ops por ciclo<sup>27</sup>. Por último, el bloque BPU es la unidad de predicción de saltos, y se encarga de detectar la dirección de destino de los diferentes saltos<sup>28</sup> y de continuar la descodificación en la dirección prevista.

Es importante notar que los bloques que se encargan de enviar información a la *IDQ* son mutuamente excluyentes, de forma que, si el *MSROM* se requiere debido a la necesidad de

<sup>&</sup>lt;sup>24</sup> En los procesadores Intel, la caché L1 se divide en dos partes, una para datos y otra para instrucciones. La caché de instrucciones suele tener un tamaño de 32Kb, una línea de caché de 64 bytes, y ser asociativa por conjuntos de ocho vías.

<sup>&</sup>lt;sup>25</sup> Entre los bloques *PreDecode* y *Decode* existe una cola de instrucciones que permite al procesador continuar calculando la posición de instrucciones con cierta independencia de la velocidad de descodificación.

<sup>&</sup>lt;sup>26</sup> MicroSequencer ROM

<sup>&</sup>lt;sup>27</sup> Los anchos de banda mencionados en este apartado coinciden con la arquitectura *SkyLake*, introducida en 2015. En arquitecturas anteriores, el ancho de banda del *Decoder* y del *DSB* solía ser de cuatro μops por ciclo. Estos valores, como se puede ver, no cambian excesivamente entre microarquitecturas, siendo el tamaño de la *IDQ* un valor mucho más variable.

<sup>&</sup>lt;sup>28</sup> Incluyendo saltos condicionales, incondicionales, llamadas a funciones, retorno de funciones, etc.

descodificar una instrucción compleja, entonces los bloques *Decode* y *DSB* están inactivos, reduciendo el rendimiento del *front-end* a cuatro *uops* por ciclo.

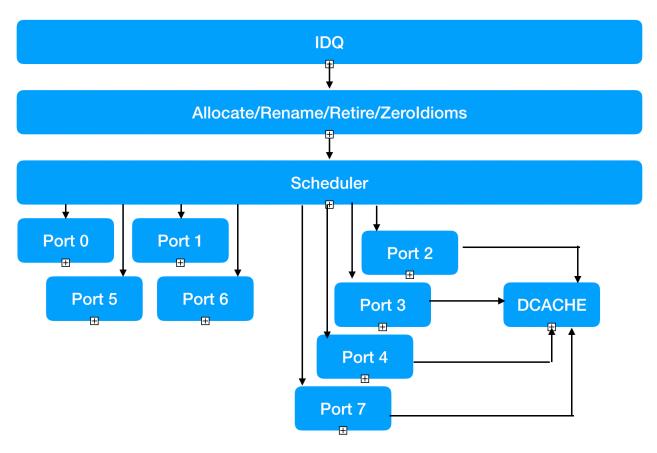

Fig 2: Visión esquemática del back-end

Como se puede apreciar, el rendimiento del *front-end* depende del tipo de instrucciones que aparecen en el programa, de su orden, de su alineamiento, de si la memoria en la que se encuentran almacenados se encuentra presente en la caché, o de si se han descodificado recientemente y están presentes en el *DSB*. Todos estos detalles pueden ser controlados en una aplicación, controlando el rendimiento del *front-end* y, por ende, el tiempo de ejecución de un trozo de código.

El contenido de la IDQ es consumido por un bloque denominado allocate/rename, que cumple varias funciones y es la interfaz entre el front-end que se funciona basado en el orden establecido por el programa, y el back-end que funciona basado en el orden establecido por las dependencias de los datos. Simplificando mucho su funcionalidad, se puede decir que se encarga de reordenar los  $\mu$ ops según el flujo de datos, de forma que puedan ser ejecutados tan pronto como los datos de los que dependen estén disponibles, y de enviarlos al planificador para su ejecución. También se encarga de retirar las instrucciones, una vez que éstas han sido ejecutadas<sup>29</sup>.

El bloque *allocate/rename* está asociado a varias optimizaciones como la detección de bucles, llamada *LSD*<sup>30</sup>, y que consiste en la detección de bucles lo suficientemente pequeños como para poder estar almacenados dentro de la *IDQ*. Cuando estos bucles se detectan, los *uops* pueden

<sup>&</sup>lt;sup>29</sup> Hacer los resultados de su ejecución visible a nivel arquitectónico. Este proceso tiene lugar en el orden en el que las instrucciones aparecen en el programa.

<sup>30</sup> Loop Stream Detector

servirse directamente desde la *IDQ* sin que sea necesario seguir descodificando instrucciones. Otra optimización llevada a cabo por la *IDQ*, y que es quizás más interesante por ser mucho más común son los llamados idiomas cero. Los idiomas cero son optimizaciones que reconocen una instrucción cuyo objetivo es hacer que el contenido de un registro sea cero. Cuando dicha instrucción es detectada, la operación se lleva a cabo directamente en este bloque, sin requerir la participación del planificador ni de los puertos de ejecución. El bloque *allocate/rename* es capaz de encargarse de la ejecución de dicha instrucción dado que conlleva básicamente un renombrado asociando un registro de la arquitectura con un registro microarquitectónico que contiene el valor 0. Cuando una instrucción puede ejecutarse sin la necesidad de un puerto de ejecución se dice que tiene latencia<sup>31</sup> cero.

Como se puede observar, existen diversos aspectos de la implementación de este bloque que tienen un impacto en el tiempo de ejecución en las instrucciones de un programa. Una operación *XOR*, requerirá menos tiempo en caso de que sus argumentos coinciden (Idioma cero). Es probable que dichas diferencias no estén modeladas adecuadamente en un emulador, de forma que se puedan usar como mecanismo de detección de emulación.

El planificador es el componente encargado de enviar los uops a las unidades de ejecución. denominadas puertos, que son los componentes que ejecutan la acción indicada por el uop. Los procesadores relativamente modernos cuentan con ocho puertos, cada una con diferentes capacidades de ejecución. Por ejemplo, la capacidad de leer y/o escribir datos en memoria suele ser proporcionada por puertos que no tienen la capacidad de llevar a cabo operaciones aritmético lógicas, como se muestra en la figura 2, donde solo los puertos dos, tres, cuatro y siete acceden a la caché de datos. Normalmente, no todos los puertos que acceden a la caché pueden leer y escribir. Por ejemplo, en arquitectas anteriores a la Sandy Bridge<sup>32</sup>, el único puerto capaz de realizar lecturas de memoria era el puerto dos, de forma que el procesador podía realizar un máximo de una lectura de memoria en cada ciclo. A partir de la microarquitectura Sandy Bridge, los puertos dos y tres tienen capacidad de lectura, de forma que el ancho de banda de lectura se duplica, proporcionando un ancho de banda típico de 96 bytes por ciclo (64 bytes leídos y 32 bytes escritos). Además, el procesador cuenta con el espacio de almacenamiento necesario para permitir que varias instrucciones de acceso a memoria estén ejecutándose en paralelo en un momento dado. Este número suele aumentar con cada nueva implementación de la arquitectura. Por ejemplo, la microarquitectura Nehalem<sup>33</sup> permite 32 accesos de escritura y 48 accesos de lectura concurrentes.

Los puertos cero, uno, cinco y seis tampoco son iguales entre sí. Todos ellos pueden llevar a cabo operaciones aritmético lógicas simples, pero no todos ellos pueden llevar a cabo operaciones complejas, como por ejemplo la división, operación que está normalmente disponible solamente en el puerto cero. Por lo tanto, el procesador ejecuta las operaciones de división en serie. Este hecho también se puede apreciar revisando la información sobre la latencia y el rendimiento<sup>34</sup> de las instrucciones, donde se indica que, en el caso de la división, la latencia y el rendimiento coinciden.

El tiempo de ejecución de un conjunto de instrucciones depende, entonces, de las dependencias de sus datos, de la disponibilidad de los puertos de ejecución necesarios, del ancho de banda del procesador, etc. Todos estos detalles de implementación pueden, de nuevo, ser explotados para detectar discrepancias en el tiempo de ejecución de diversos trozos de código.

$<sup>^{31}</sup>$  El número de ciclos de procesador que requiere la ejecución de todos los  $\mu$ ops de la instrucción. Normalmente este valor es aproximado, y no tiene en cuenta retardos potenciales como por ejemplo fallos de caché.

<sup>32</sup> Introducida en 2011

<sup>33</sup> Introducida en 2008

<sup>&</sup>lt;sup>34</sup> El número aproximado de ciclos de procesador necesarios desde que una instrucción comienza a ejecutarse hasta que la misma instrucción puede comenzar a ejecutarse nuevamente.

#### 6.3. Consideraciones iniciales

Se han barajado diversas opciones a la hora de definir la estructura general de los diversos ejemplos de detección.

Se descarto el crear una aplicación completa que pudiese ser ejecutada tanto en un entorno real como en el entorno emulado puesto que ello requeriría una configuración relativamente compleja del emulador, sin que aportase valor alguno al objetivo del trabajo. La complejidad en la configuración del emulador viene dada, en gran medida, por la necesidad de crear un entorno de ejecución adecuado y de un mecanismo de carga del fichero ejecutable en el emulador.

La siguiente opción, que también fue descartada, se basaba en la idea de crear dos ficheros ejecutables diferentes. El primero de ellos se ejecutaría en el entorno real, conteniendo una función con el código de detección de emulación. El segundo ejecutable sería el host para el emulador, que obtendría el código de la función de detección del primer ejecutable, y la ejecutaría dentro del emulador. Para obtener el código de la función de detección se usaría el framework de ingeniería inversa *Radare*<sup>35</sup>. La única

```

EMU = emulate1

PROG = example1

RADARE = radare2

TEST_HEADER = emublk.h

LDFLAGS2 += $(LDFLAGS) -lm -lunicorn

RADAREFLAGS = -qc "aaa;s sym._detect;bf sym._detect;b-1;pc> $(TEST_HEADER)"

PROG_OBJS = detect.o main.o

all: $(EMU)

clean:

@rm -f $(PROG) $(PROG_OBJS) $(TEST_HEADER) $(EMU) $(EMU).o

%.o: %.c

@$(CC) $(CFLAGS) -o $@ -c $<

$(PROG): $(PROG_OBJS)

@$(CC) $^(LDFLAGS) -o $@

$(TEST_HEADER): $(PROG)

@$(RADARE) $(RADAREFLAGS) $(PROG) ||:

$(EMU).o: $(TEST_HEADER)

@$(CC) $(CFLAGS) -o $@ -c $(EMU).c

$(EMU): $(EMU).o

@$(CC) $(CFLAGS) $^ $(LDFLAGS2) -o $@

.PHONY: all clean</pre>

```

Fig 3: Makefile usando Radare

limitación notable impuesta a la implementación del código de la función de detección sería que debería ser independiente de la posición. La figura 3 muestra el fichero *Makefile* para la compilación de ambos ejecutables, donde la función de detección copiada de un ejecutable a otro se llama *detect*. La principal ventaja de esta opción es que permitiría implementar los ejemplos en cualquier lenguaje de programación compilado. Esta opción se descartó dado que los lenguajes de medio y alto nivel no resultan lo suficientemente expresivos como para controlar el código binario generado con el nivel de detalle necesario en este trabajo. Una opción habría sido utilizar un compilador con funciones intrínsecas que proporcionase un acceso más directo a las capacidades del procesador<sup>36</sup>, pero no se ha visto ventaja alguna entre esta opción y escribir el código directamente en ensamblador.

Una vez que la necesidad de implementar los ejemplos de detección directamente en ensamblador se hizo evidente, se optó por una tercera opción, en la que se genera un solo ejecutable conteniendo una función de detección implementada en ensamblador<sup>37</sup>, que es ejecutada y después emulada. Al igual que en el caso anterior, la limitación principal impuesta al código de la función de detección es que debe ser independiente de su posición. La figura 4 muestra el contenido de un fichero *Makefile* utilizado para los ejemplos.

<sup>35</sup> https://rada.re/r/

<sup>&</sup>lt;sup>36</sup> El compilador de C/C++ de Intel es un notable ejemplo, con funciones intrínsecas permitiendo ejecutar prácticamente cualquier instrucción en ensamblador de forma directa.

<sup>&</sup>lt;sup>37</sup> Nótese que la elección del ensamblador como lenguaje para implementar la función de detección habilita esta opción, puesto que no existe un mecanismo fiable para conocer el tamaño de una función en C/C++. En general, ni siquiera se puede asumir que una función será compilada generando un bloque de código compacto. En cambio, en ensamblador es posible conocer el tamaño de la función, y asegurarse de que su estructura es la esperada.

Todos los ejemplos comparten, entonces, una estructura similar. Un fichero en ensamblador, llamado *detect.asm*, y que contiene dos funciones: La función *detect*, que lleva a cabo la detección, retornando un valor *booleano* que indica si la emulación ha sido detectada, y la función *detect\_length*, que indica el tamaño de la función *detect*, y que es usada para copiar la función de detección al emulador. El fichero de cabecera *detect.h*, que permite utilizar la función *detect* en C/C++. El fichero *main.c*, que es el esqueleto de la aplicación, y un fichero *Makefile* para llevar a cabo la compilación lo más cómodamente posible.

Se ha optado por minimizar el proceso de configuración del emulador, de forma que la emulación tan solo copia la función dentro del entorno del emulador y trata de ejecutarla. Al no llevarse a cabo una configuración adecuada, se añade una nueva restricción a la implementación de las rutinas de detección: No pueden usar ninguna instrucción que interactúe con la pila, puesto que ésta no ha sido inicializada debidamente. Por convenio, se decide que la función detect solo puede tener un punto de retorno, y debe ser la última instrucción de la función. El emulador comienza su ejecución en la primera instrucción de la función detect. La última instrucción (el retorno) no se copia al emulador, garantizando que la pila no se usa. Por convenio, también se decide que en caso de que la rutina de detección requiera de un área de memoria, esta será proporcionada como argumento. Esta decisión ánade una nueva restricción a la rutina de detección: El convenio de llamada utilizado por la función debe ser del tipo fastcall38.

```

PROG = example$(EXAMPLE)

NASM = nasm

UNAME = \$(shell uname -s)

ifeq ($(UNAME),Linux)

NASMFLAGS = -g - f elf64

LDFLAGS += -lpthread

ifeq ($(UNAME),Darwin)

NASMFLAGS = -g - f macho64

LDFLAGS += -lm -lunicorn

CFLAGS += -03 -Wall -DNDEBUG

PROG_OBJS = detect.o main.o

all: $(PROG)

@rm -f $(PROG) $(PROG OBJS)

%.o: %.c $(HEADERS)

%.o: %.asm

@$(NASM) $(NASMFLAGS) $<

$(PROG): $(PROG_OBJS)

```

Fig 4: Ejemplo de Makefile

En cuanto al entorno de trabajo, se han utilizado dos entornos diferentes para llevar a cabo las diferentes pruebas. El entorno principal, donde se ha llevado a cabo el grueso del trabajo, cuenta con un procesador *Intel Core i5-7400*, con microarquitectura *Kaby Lake*<sup>39</sup>. El sistema operativo usado es *MacOs Mojave*. El segundo entorno, utilizado solamente para llevar a cabo un segundo test de las rutinas de detección, cuenta con un procesador Intel Core i5-5200U, con microarquitectura *Broadwell*<sup>40</sup>, y con un sistema operativo *Debian 9.6*. También se ha usado una máquina virtual, usando el sistema *VirtualBox*, virtualizando un sistema operativo *Debian 9.6*, y ejecutándose en el entorno principal. El objetivo del entorno virtual fue el poder llevar a cabo pruebas de validez de forma ágil.

La estructura de la función de detección en los diferentes ejemplos es prácticamente siempre la misma. Dos bloques de código se ejecutan, calculando sus tiempos de ejecución. Los bloques de código están diseñados de forma que el bloque que se ejecuta más rápidamente en el entorno real se pasará a ser el que se ejecuta más lentamente en el entorno emulado. En los casos en que los ejemplos no se correspondan con este esquema, se indicará y se explicará la estructura de la función de detección. Ha de hacerse notar que los bloques de código se ejecutan una única vez. Cada uno de los ejemplos proporcionados tienen una probabilidad de detección errónea o de no

<sup>&</sup>lt;sup>38</sup> Todos los sistemas x64 usan convenios de llamadas a funciones de tipo *fastcall*. Esta restricción se ha mencionado para proporcionar una lista completa de restricciones, pero es un mero formalismo. En concreto, el entorno de trabajo principal usa la convención *System V AMD64 ABI*, que se puede consultar en <a href="https://github.com/hjl-tools/x86-psABI/wiki/X86-psABI">https://github.com/hjl-tools/x86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86-psABI/wiki/X86

<sup>39</sup> Introducida en 2017

<sup>&</sup>lt;sup>40</sup> Introducida en 2015

detección<sup>41</sup>. Una estructura más compleja, ejecutando los bloques mencionados varias veces, combinando diversos conceptos, etc. reduciría la probabilidad de error drásticamente. Se ha optado, por el contrario, por ejemplos más sintéticos, que muestren los conceptos utilizados con mayor claridad.

```

mfence

rdtsc

sal rdx, 32

mov rsi, rdx

add rsi, rax

```

Fig 5: Ejemplo de toma de tiempo, almacenándolo en psi

A la hora de analizar la probabilidad de error de los diversos ejemplos, se ha ejecutado cada uno de ellos un total de un millón de veces. Normalmente, la probabilidad de error se sitúa por debajo del 1%. En caso de que la probabilidad de error sea mayor, se indicará explícitamente.

El cálculo de los tiempos de ejecución se ha llevado a cabo utilizando la función *RDTSC*<sup>42</sup>. La figura 5 muestra un ejemplo de una toma de tiempo, almacenando el resultado en el registro *RSI*. La instrucción *RDTSC* no serializa la ejecución, por lo que instrucciones anteriores al *RDTSC* podrían estar aun ejecutándose, o instrucciones posteriores podrían haber comenzado su ejecución. Para atajar este problema, se sitúa una instrucción *MFENCE*<sup>43</sup> antes del *RDTSC*. Una última limitación impuesta a los ejemplos de detección implementados es que deben funcionar correctamente en modo usuario. Si un método de detección requiriese de la ejecución de una instrucción privilegiada, la aplicación de dicho método se vería seriamente limitado, hasta el punto de resultar

prácticamente inútil desde el punto de vista práctico.

```

/example1

[*] Executing emulation detection function

[+] Emulation not detected

[*] Emulating emulation detection function

[+] Emulation detected

```

Fig 6: Resultado de un ejemplo de detección

# 6.4. Ejemplo 1: Rendimiento de las instrucciones

El manual de optimización de Intel [In16] documenta, como ya se ha mencionado, la latencia y el rendimiento de cada una de las instrucciones. Estos valores son aproximados, pero cuanto más distantes sean, especialmente el rendimiento de la instrucción, mayor será la probabilidad de poder observar dicha diferencia de forma empírica.

Hay que tener en cuenta es que el resultado de una instrucción tiene que ser computado tanto durante la emulación como durante la ejecución real. En los casos en los que la emulación y el sistema que ejecuta el emulador comparten la misma arquitectura puede observarse un comportamiento similar, dado que el emulador puede ejecutar efectivamente la instrucción emulada.

<sup>&</sup>lt;sup>41</sup> Detección errónea se refiere a reportar que se detecta emulación cuando la función de detección se ejecuta en el entorno real. La no detección se refiere a no reportar la detección de emulación cuando la función de detección está siendo emulada.

<sup>&</sup>lt;sup>42</sup> La instrucción *RDTSC* lee el contenido del contador de marca de tiempos, un registro que se incrementa con cada ciclo del procesador.

<sup>&</sup>lt;sup>43</sup> MFENCE serializa las instrucciones de lectura y escritura de datos en memoria. El manual de intel recomiendo usar la instrucción *LFENCE* antes del *RDTSC*. En este caso, la implementación propuesta sigue la línea de la implementación del kernel de Linux, que usa *MFENCE* en algunos casos. Para más detalles, se pueden consultar los ficheros <a href="https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/arch/x86/include/asm/barrier.h?h=v4.20-rc7">https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/arch/x86/include/asm/msr.h?</a> <a href="https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/arch/x86/include/asm/msr.h?h=v4.20-rc7">https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/arch/x86/include/asm/msr.h?h=v4.20-rc7</a>

Un emulador puede llegar a traducir cada instrucción emulada en decenas o cientos de instrucciones ejecutadas, por lo que esta posibilidad es relativamente pequeña, pero se incrementa notablemente si el emulador implementa ciertas optimizaciones, como por ejemplo la traducción dinámica de código.

Una opción interesante a la hora de diseñar una detección es utilizar instrucciones que además de llevar a cabo una operación, tengan otros efectos microarquitectónicos concretos, o instrucciones que sean utilizadas para controlar algún aspecto del estado microarquitectónico sin modificar el estado arquitectónico. Este ejemplo se basa en el segundo caso, seleccionando las instrucciones *LFENCE* y *MFENCE*. Ambas instrucciones son barreras de memoria, y como tales sirven para serializar las operaciones de acceso a memoria, y son de utilidad en implementaciones multihilo. En principio, un emulador estándar solo necesita aceptar las instrucciones, pudiendo implementarlas como operaciones nulas. La instrucción *MFENCE* es mucho más lenta que *LFENCE*. Además, la instrucción *MFENCE* hace que el código al que acompaña se ejecute más lentamente que en el caso de *LFENCE*. Esto se debe a que la serialización impuesta por *MFENCE* se aplica a todas las operaciones de acceso a memoria, mientras que en el caso de *LFENCE* solo se aplica a las operaciones de lectura.

La figura 7 muestra dos bucles. El bucle 1 ejecuta una instrucción *LFENCE*, mientras que el bucle 2 ejecuta una instrucción *MFENCE*. La instrucción *XOR EAX, EAX* se añade al bucle para que éste lleve a cabo alguna computación extra. Nótese que la instrucción en el bucle no es serializada por ninguna de las dos barreras de memoria.

```

loop1:

lfence

xor rax, rax

dec r8

jne .loop1

.loop2:

mfence

xor rax, rax

dec r8

jne .loop2

```

Fig 7: Rendimiento de las instrucciones

En la ejecución de estos dos bucles en la máquina real se puede apreciar que el bucle número dos es más lento que el bucle número 1, lo cual es consistente con los datos proporcionados por la documentación del fabricante. En cambio, cuando estos dos bucles se ejecutan dentro del emulador, el bucle número 1 es más lento que el bucle número dos. Además, este ejemplo de detección es uno de los más estables, con un ratio de error de aproximadamente un 0,1%. Aunque no se muestra en la figura, los bucles son ejecutados un total de 100 veces. El objetivo de ejecutar las instrucciones en un bucle es el de ejecutar suficientes instrucciones como para que las mediciones de tiempos sean lo más estables posibles, pero sin ejecutar más instrucciones de las estrictamente necesarias.

## 6.5. Ejemplo 2: Optimizaciones en allocate/rename

El bloque *allocate/rename* funciona como interfaz entre el *front-end* y el *back-end* del procesador. Ya se han mencionado los idiomas cero como ejemplo de optimización llevada a cabo por este componente, y que podrían ser usados para diseñar un mecanismo de detección de emulación. En este caso, se va a utilizar una optimización similar disponible en dicho bloque. A partir de la microarquitectura *Ivy Bridge*<sup>44</sup>, ciertas operaciones de copia se ejecutan directamente en este bloque. En concreto, muchas de las copias en las que sus dos operandos son registros son completadas directamente en el bloque allocate/rename. Una limitación interesante es que el

\_

<sup>44</sup> Introducida en 2012

registro origen y el registro destino no pueden coincidir, en cuyo caso la instrucción es enviada al planificador para su ejecución<sup>45</sup>.

La figura 8 muestra los dos bucles usados en este caso para la detección de emulación. El bucle 1 ejecuta varias copias entre registros, mientras que el bucle 2 tiene el mismo número de copias, pero los operados de cada una de ellas siempre coincide. Como se ha indicado, en un procesador real el bucle 1 se ejecuta más rápidamente que el bucle 2. Nótese, además, que el cuerpo de bucle es lo suficientemente pequeño como para que se almacene en la *IDQ*, y pueda ser optimizado por el *LSD*. De esta forma, nos aseguramos que el rendimiento del *front-end* no tendrá impacto alguno en la ejecución de los bucles.

```

mov r8, 128

.loop1:

mov rax, rbx

mov rcx, rbx

mov rdx, rbx

mov rax, rbx

mov rax, rbx

mov rax, rbx

mov rax, rbx

mov r9, rbx

dec r8

jne .loop1

mov r8, 128

.loop2:

mov rax, rax

mov rcx, rcx

mov rdx, rdx

mov rax, rax

mov r9, r9

dec r8

jne .loop2

```

Fig 8: Instrucciones con latencia cero en el bucle 1

Cuando estos dos bucles son emulados, el emulador no tiene en cuenta los aspectos mencionados, de forma que es el bucle 1 el que se ejecuta más lentamente.

## 6.6. Ejemplo 3: Super escalar

El siguiente es uno de los ejemplos más interesantes. En este caso, la estructura de la función de detección no sigue la estructura típica. El objetivo de este ejemplo es el detectar la emulación basándose en el hecho de que la microarquitectura del procesador es super escalar. Se ha comentado con anterioridad que los procesadores modernos cuentan con dos puertos para llevar

```

mov rax, [rdi]

mfence

rdtsc

sal rdx, 32

mov rsi, rdx

add rsi, rax

times 256 mov rax, [rdi]

mfence

rdtsc

sal rdx, 32

add rdx, rax

sub rdx, rsi

sar rdx, 8

mov r9, rdx

```

Fig 9: Calculo del tiempo promedio de carga

a cabo una operación de lectura de memoria. Por lo tanto, un grupo de operaciones de lectura en memoria se podrán ejecutar de dos en dos siempre que no existan dependencias de datos. El ancho de banda también puede suponer una limitación, por lo que es crucial que no se supere el ancho de banda para la lectura, que es de 64 bytes.

La figura 9 muestra la primera fase de la lógica de detección de emulación. Su objetivo es calcular el tiempo de ejecución promedio de un conjunto de accesos de lectura, que por simplicidad son siempre un acceso a la misma dirección de memoria. Se comienza llevando a cabo una lectura de la dirección de memoria que se usará como zona de acceso. Esta primera lectura garantiza que la memoria se encuentre en la caché, evitando que un fallo de caché pueda alterar los cálculos. Después, se toma el tiempo inicial,

<sup>&</sup>lt;sup>45</sup> Puede sonar extraño que una instrucción que no tiene efecto alguno sea enviada al planificador. Este comportamiento se debe a que la instrucción *NOP* es la codificación 0x90, que es en realidad una copia del contenido de *RAX* en *RAX*. Si esta instrucción no se enviase al planificador y pasase a tener latencia cero, el comportamiento de muchos bucles de espera activa que usan *NOP* en vez de *PAUSE* cambiaría drásticamente. Nótese, además, que la codificación de *PAUSE* coincide con un *NOP* con un prefijo.

y se ejecuta la operación de carga un total de 256 veces. Finalmente, se vuelve a tomar el tiempo, calculando el tiempo promedio por instrucción, que se almacena en el registro R9. Como se puede apreciar, no se ha introducido ningún bucle, sino que se han generado las 256 instrucciones. El objetivo es evitar que la introducción de instrucciones de control de flujo, en especial la predicción errónea asociada a la salida del bucle, alteren el cálculo del tiempo promedio.

La ejecución de cada instrucción lee ocho bytes de memoria. Se asume que *RDI* contiene una dirección correctamente alineada, de forma que el contenido leído esté alojado en una única línea de la caché. Se espera que el procesador pueda utilizar los dos puertos disponibles para ejecutar las operaciones de carga. Un aspecto interesante a tener en cuenta es que el código actual, tal y como se muestra en la figura 9, presenta un problema menor. Durante la ejecución del bloque de instrucciones usadas para calcular el tiempo promedio, el *prefetcher* cargará datos extra en la cache de datos L1. La documentación existente no explica claramente si esta acción puede afectar los tiempos de ejecución<sup>46</sup>. Llevar a cabo tres accesos a la dirección de memoria en cuestión antes de ejecutar el conjunto de instrucciones destinado a tomar la medición debería solucionar el problema. De todas formas, la detección de emulación funciona correctamente sin llevar a cabo modificación alguna, por lo que se ha optado por dejar el código sin modificar.

```

mfence

rdtsc

sal rdx, 32

mov rsi, rdx

add rsi, rax

mov rax, [rdi]

mfence

rdtsc

sal rdx, 32

add rdx, rax

sub rdx, rsi

```

Fig 10: Tomar el tiempo de una instrucción de lectura

La figura 10 muestra la segunda parte de la lógica de detección. Como se puede apreciar, se trata. simplemente, de tomar el tiempo de ejecución de una sola instrucción de lectura de memoria. La instrucción se encuentra precedida y sucedida por instrucciones MFENCE, sin que existan otras operaciones de acceso a memoria en el bloque de código limitado por las barreras de memoria. Por lo tanto, durante la ejecución de ese bloque, los puertos de ejecución que proporcionan acceso a memoria no se usarán, a excepción del puerto que se encarque de la ejecución de la instrucción de lectura. En la fase anterior, los dos puertos de ejecución con capacidad para leer datos de memoria estaban en uso, de forma que el tiempo promedio de ejecución calculado en el bloque anterior debe ser considerablemente menor que el tiempo

necesario para ejecutar la instrucción mostrada en la Figura 10.

Al ejecutar la rutina de detección en la máquina real, se puede observar el comportamiento esperado. Sin embargo, al emular la rutina de detección, el tiempo de ejecución de la instrucción de carga mostrada en la figura 10 es menor que el tiempo promedio calculado al ejecutar el código mostrado en la figura 9.

# 6.7. Ejemplo 4: Comportamiento de la Caché

Utilizar el estado de la caché y su impacto en los tiempos de ejecución de las instrucciones de lectura y escritura en memoria es un concepto que ya ha sido tratado en trabajos previos. En este trabajo, por lo tanto, no se ahonda en los aspectos ya estudiados, pero se presentan otros ejemplos de funcionalidades asociadas a la caché y que también pueden ser utilizadas como mecanismo de detección de emulación.

Como es común en todos los sistemas con caché, el primer acceso a una dirección de memoria que no se encuentre en la caché lleva asociado un coste extra. En este ejemplo los dos bloques de código son exactamente el mismo, como se puede apreciar en la figura 11.

<sup>&</sup>lt;sup>46</sup> Tampoco deja claro cuál es el funcionamiento esperado en este caso. La documentación indica que el *prefectcher* de datos de la caché L1 (*DCU Prefetcher*) se activa cuando se llevan a cabo accesos a direcciones de memoria crecientes. Sin embargo se indica en un ejemplo que tres accesos consecutivos a la misma dirección de memoria activarían al *prefetcher L1*.

```

mov rdi, r8

mov rcx, 256

.loop2:

mov rax, [rdi]

add rdi, 8

sub rcx, 8

jne .loop2

```

```

mov rdi, r8

mov rcx, 256

.loop3:

mov rax, [rdi]

add rdi, 8

sub rcx, 8

jne .loop3

```

Fig 11: Efecto de la caché en los tiempos de ejecución

En este caso los bucles están etiquetados como bucle 2, que es el primero en ejecutarse, y bucle 3, que es el segundo en ejecutarse. El buffer al que apunta *R8* no está en la caché, por lo que el bucle 2 debe ejecutarse más lentamente que el bucle 3. Cuando el bucle 2 comienza a ejecutarse, los accesos a memoria con un patrón de direcciones crecientes a distancias constantes activará el *prefetcher*, lo que hará que la diferencia de tiempos no sea excesivamente grande. La diferencia es, no obstante, suficiente como para que la detección funcione.

Estos dos bucles por sí solos no son suficiente para generar una detección. El emulador seleccionado se comporta de la misma forma que lo hace el hardware real. En la figura 12 se muestra el contenido del primer bucle. En él se puede ver que el buffer es inicializado. La

```

mov r8, rdi

mov rcx, 256

.loop1:

movntps [rdi], xmm0

movntps [rdi+16], xmm0

movntps [rdi+32], xmm0

movntps [rdi+48], xmm0

add rdi,64

sub rcx,64

jne .loop1

```

Fig 12: Inicialización sin tocar la caché

instrucción utilizada para inicializar el buffer es *MOVNTPS*, que es una de las instrucciones no temporales. Este tipo de instrucciones permiten controlar el comportamiento de la caché al mismo tiempo que se lleva a cabo una lectura o escritura. En este caso, el buffer es inicializado, pero la caché no se actualiza basándose en el acceso a memoria. Es interesante notar que a no ser que un emulador quiera proporcionar información de conteo de tiempos precisa, no tiene por qué tener en cuenta las implicaciones microarquitectónicas de las instrucciones no temporales. Si el objetivo es emular solo el comportamiento, las instrucciones no temporales pueden ser implementadas exactamente

como las funciones de acceso a memoria estándar.

Entonces, la lógica de este ejemplo es cómo se explica a continuación. En un equipo real, el primer bucle, que utiliza instrucciones no temporales no modifica el estado de la caché, de forma que el bucle número 2 incurrirá en fallos de caché, haciendo dicho bucle notablemente más lento que el bucle número 3. En el caso del sistema emulado, o bien los dos bloques se ejecutan en tiempos similares al no tener encuesta ningún aspecto de la caché, o el bucle número 1 se implementa en base a operaciones estándar, haciendo que el bucle número 2 no incurra en fallos de caché, y haciendo, por lo tanto, que los bucles 2 y 3 se ejecuten en tiempos similares. Este segundo escenario es el que provoca la detección de emulación en el caso del emulador seleccionado.

# 6.8. Ejemplo 5: Comportamiento de la Caché (2)

La caché cuenta con *prefetchers* hardware, que carga en la caché de datos de forma automática, asumiendo que dichos datos van a ser necesarios. Esta decisión se hace en base a los patrones de acceso a memoria. En el caso de la caché L1, el *prefetcher* es activado cuando se detectan accesos a direcciones de memoria en dirección ascendiente. En el caso de la caché L2, su *prefetcher* es más complejo y puede ser activado por accesos a memoria en direcciones tanto ascendientes como descendientes, además de llevar a cabo lecturas adicionales basándose en las líneas de caché presentes en la caché L1.

```

xor rax, rax

xor rcx, rcx

.loop2:

fld qword [rdi + rax + 64]

mov eax, [rdi + rcx*4]

prefetcht0 [rdi + rax + 64]

mov r8, 64

.loop22:

fldpi

fdiv

dec r8

jne .loop22

inc rcx

cmp rcx, 16

jne .loop2

```

```

xor rax, rax

xor rcx, rcx

.loop3:

fld qword [rdi+rax + 64 + 1024]

mov eax, [rdi + rcx*4]

mov r8, 64

.loop33:

fldpi

fdiv

dec r8

jne .loop33

inc rcx

cmp rcx, 16

jne .loop3

```

Fig 13: prefetching

Además de los *prefetchers* hardware, la arquitectura proporciona la opción de llevar a cabo *prefetching* por software, de forma que se puede indicar al procesador que cargue unos datos concretos en la caché. Al igual que en el ejemplo 1, este tipo de instrucciones, que tan solo se encargan de modificar el estado de la caché, pueden ser ignoradas por un emulador, proporcionando una posibilidad de detección.

La figura 13 muestra dos bloques de código. En el bucle 2 se utiliza el *prefetcher* software por medio de la instrucción *PREFETCHO*. El buffer de datos usado, cuya dirección se almacena en el registro *RDI*, no está en la caché. El buffer contiene en su inicio una serie de números aleatorios, de forma que la instrucción *FLD* cargará en cada iteración un dato de una posición de memoria, sin que el *prefetcher* hardware pueda predecirla ni cargar el bloque de memoria por adelantado. El bucle 2 usa el *prefetcher* software para que el sistema cargue los datos requeridos en la siguiente iteración en la caché mientras ejecuta el código de la iteración actual.

El bucle 3 no utiliza el *prefetcher*, de forma que la instrucción *FLD* siempre tendrá que esperar a que los datos sean leídos de la memoria principal. En este ejemplo el tiempo de la computación llevada a cabo con los datos leídos en un ciclo dado tiene que ser mayor que el tiempo de ejecución de la instrucción *PREFETCHO*. De no ser así, obtendríamos el efecto contrario, siendo el bucle 1 más lento que el bucle 2.

Existe un primer bucle que no es mostrado, que inicializa el buffer. La inicialización del buffer es necesaria para asegurar que las operaciones en ambos bucles se ejecutan con los mismos operandos<sup>47</sup>.

Éste es uno de los ejemplos menos estable, con un ratio de error de aproximadamente el tres por ciento. El ejemplo también funciona correctamente sin el bucle de inicialización, pero el ratio de error aumenta ligeramente, llegando a fallar en un cinco por ciento de los casos.

# 6.9. Ejemplo 6: Reenvío de datos

Una de las optimizaciones más importantes en los procesadores de Intel, y que no se ha mencionado hasta ahora, es el reenvío de datos. Cuando una instrucción escribe un dato en memoria, y otra instrucción posterior lee dicho dato de memoria, el procesador es capaz de enviar el dato directamente de una instrucción a la siguiente, sin necesidad de esperar a que los accesos a memoria se completen.

<sup>&</sup>lt;sup>47</sup> El valor de los operandos es uno de los factores que define el tiempo de ejecución de las divisiones, tanto de números enteros como en coma flotante.

```

xor ecx, ecx

.loop1:

mov [rdi + rcx * 8], rcx

mov rcx, [rdi + rcx * 8]

inc rcx

cmp rcx, 64

jne .loop1

```

```

Fig 14: Reenvío de datos entre escritura y lectura

```

```

xor ecx, ecx

.loop2:

mov [rdi + rcx * 8], ecx

mov dword [rdi + rcx * 8 + 4], 0

mov rcx, [rdi + rcx * 8]

inc rcx

cmp rcx, 64

jne .loop2

```

Existen diversas restricciones para que el reenvío de datos mencionado se pueda llevar a cabo. La mayoría de las restricciones hacen referencia a los tipos de datos reenviados, su alineamiento en memoria, y a las posiciones en las instrucciones involucradas. Este ejemplo escoge una de las limitaciones y la intenta explotar construyendo un método de detección basado en ella.

Una de las restricciones existentes es que para que un dato escrito en memoria se pueda reenviar directamente a otra instrucción que lleva a cabo su lectura es necesario que el dato haya sido escrito por una única instrucción. Por ejemplo, la escritura de cuatro bytes que conforma un *DWORD* seguida de la lectura de dicho *DWORD* no es optimizado mediante este sistema. Esta restricción será usada en este ejemplo de detección de emulación. La figura número 14 muestra los dos bucles usados en el ejemplo. El bucle 1 escribe un *QWORD* que es leído por la siguiente instrucción. En el bucle 2, la escritura del *QWORD* se lleva a cabo en dos fases, con dos instrucciones de escritura que escriben un *DWORD* cada una. Se asume que la zona de memoria a la que los dos bucles acceden ya está presente en la caché cuando éstos se ejecutan. En caso contrario, el primer bucle incurriría en un coste extra probablemente mayor que la mejora obtenida de esta optimización. También se asume que los accesos a memoria están correctamente alineados, de forma que no se incurren en costes extra debido a problemas de alineamiento.

Este ejemplo es especialmente interesante dado que podría esperarse que el bucle número dos se ejecutase más lentamente independientemente de la optimización mencionada, dado que contiene más instrucciones, lo que conlleva más trabajo para el *front-end*, y más µops que ejecutar. Lo cierto es que, cuando el bucle 1 no se aprovecha de la ventaja proporcionada por la optimización discutida en este apartado, el tiempo de ejecución de ambos bucles es prácticamente el mismo, de forma que no pueden utilizarse para la detección de emulación. Este comportamiento se puede obtener, por ejemplo, haciendo que los accesos a memoria no estén debidamente alineados. La razón por la que el tiempo de ejecución de los bucles es similar a pesar de la diferencia en el número de instrucciones se debe a dos factores. El primero es que el tiempo de ejecución del código en los bucles está limitado por el ancho de banda del procesador, de forma que el resto de factores pasan a ser prácticamente irrelevantes. El segundo es una optimización conocida como combinación de escrituras, mediante la cual el procesador ensambla escrituras múltiples en una sola escritura.

Otra cuestión interesante es el que el emulador de referencia reporta que es el primer bucle el que se ejecuta más lentamente que el segundo. Este resultado no parece muy intuitivo.

# 6.10. Ejemplo 7: Macro fusión

La macro fusión es una optimización presente en todas las microarquitecturas relativamente recientes, y de la que no se ha hablado previamente. La combinación de instrucciones consistente en una comparación seguida de un salto condicional es muy común en el código

binario. Aunque la mayoría de las instrucciones actualizan el registro de  $FLAGS^{48}$ , es difícil que dicho registro contenga los datos adecuados para controlar el flujo de la aplicación, lo que obliga a introducir instrucciones de comparación explícitas, normalmente instrucciones TEST o CMP. La macro fusión detecta esta combinación de instrucciones, generando un único  $\mu$ op. Existen varias restricciones en la aplicación de esta optimización. La alineación de las instrucciones en memoria debe ser la correcta, y no todas las combinaciones de instrucción de comparación y salto condicional permiten la macro fusión<sup>49</sup>. Por ejemplo, el salto condicional basado en el estado de los *flags* de signo y paridad (JS, JP, etc.) no se fusionan con la instrucción CMP.

```

mov rdi, r8

xor r10, r10

.loop1:

mov al, [rdi]

movzx eax, al

add r10, rax

add rdi, 1

cmp byte [rdi], cl

jge .loop1

mov rdi, r8

xor r10, r10

.loop2:

mov al, [rdi]

movzx eax, al

add r10, rax

add rdi, 1

cmp byte [rdi], cl

jge .loop2

```

Fig 15: Macro fusión

La documentación disponible relativa a la macro fusión es poco clara en algunos aspectos. Hay, de todas formas, un comentario que dice explícitamente que una comparación de un valor en memoria con un valor inmediato seguido de una instrucción *JGE* inhibe la macro fusión. El ejemplo de detección presentado se basa en el comentario que se acaba de mencionar. La figura número 15 muestra los dos bloques usados en este ejemplo de detección.

El código en el bucle suma un conjunto de valores de tipo *char* almacenados en un buffer. El valor 0 indica el final de la lista. Para comprobar si se debe seguir ejecutando el bucle, el valor actual se compara con 1, ejecutando una nueva iteración si dicho valore es mayor o igual a 1. En el primer bucle, el valor 1 ha sido almacenado en el registro *CL*, mientras que en el segundo bucle el valor de comparación se da como un valor inmediato. Se asume que el buffer al que se accede está en la caché, de forma que ninguno de los bucles incurre en fallos de caché. De acuerdo al comentario mencionado anteriormente, al ejecutar ambos bucles en un procesador real, el primer bucle debe ser el único que aprovecha la macro fusión, siendo más rápido que el segundo. En un sistema emulado, se espera que el segundo bucle sea más rápido, puesto que los registro están modelados como variables y por lo tanto es de esperar que los valores inmediatos ahorren accesos a memoria.

Las pruebas realizadas con este ejemplo muestran que los resultados son consistentes con las expectativas. El bucle número 1 es el más rápido en la máquina real, mientras que en el emulador es el segundo bucle el que se percibe como el más rápido.

<sup>&</sup>lt;sup>48</sup> Se pueden consultar ejemplos mostrados anteriormente, como el mostrado en la figura 7, donde no se lleva a cabo una comparación explícita. La instrucción *DEC* realiza una actualización parcial del registro de *FLAGS*. El salto condicional controla el flujo basándose en dicha actualización.

<sup>&</sup>lt;sup>49</sup> Es interesante notar que antes de la microarquitectura *Nehalem*, la instrucción *CMP* no podía fusionarse con las instrucciones de salto condicional asociadas a tipos de datos con signo (*JL*, *JG*, *JNL*, etc.). Esta circunstancia planteaba una disyuntiva interesante, puesto que el uso de tipos enteros sin signo podían aprovechar la macro fusión, pero al mismo tiempo en C/C++ se suelen preferir los tipos enteros con signo, puesto que su comportamiento está parcialmente definido, abriendo posibilidades para potenciales optimizaciones.

## 6.11. Ejemplo 8: Delaminación